Chip circuit fan-out method and thin film chip device

A thin-film chip and chip technology, applied in circuits, electrical components, electrical solid devices, etc., can solve the problems of reducing the cost of chip design, etc., and achieve the effect of convenient line layout, overcoming line kinks, and large layout flexibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

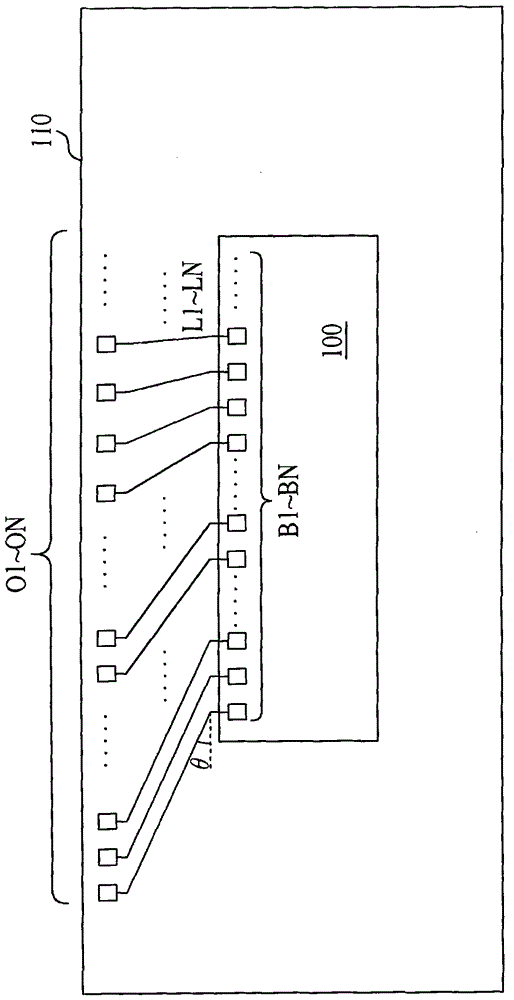

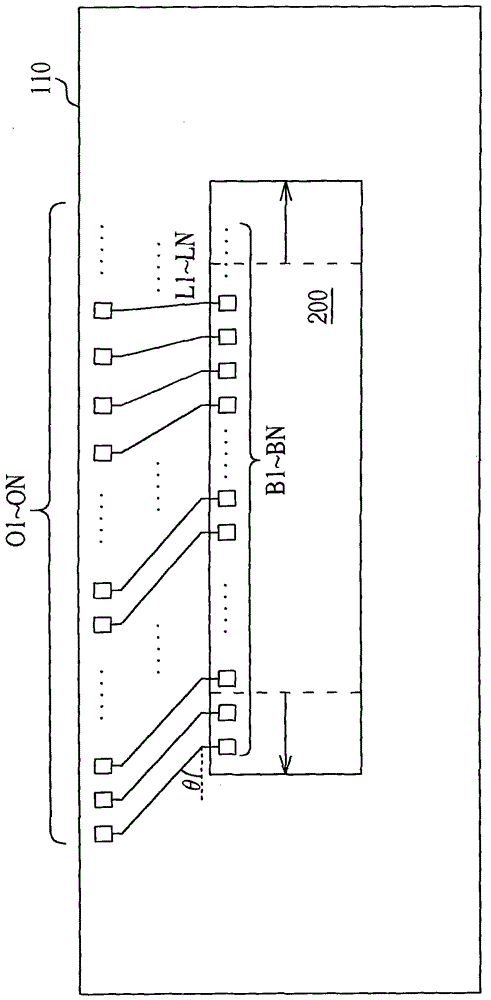

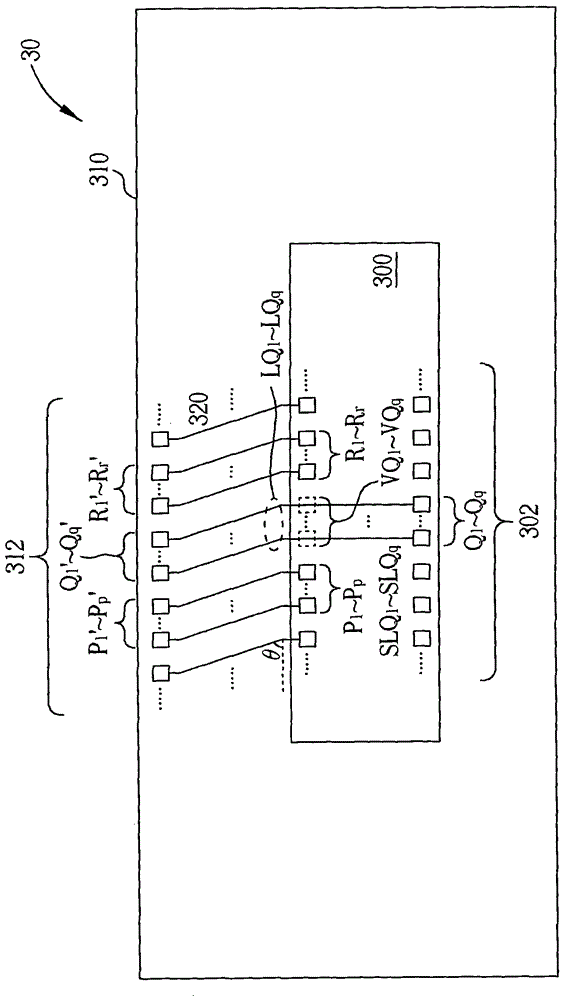

[0040] Different from the prior art that the joints of the external pins must be connected to the external protrusions in accordance with the arrangement order of the external protrusions, in the following embodiments, the joints of the external pins will not be connected in accordance with the arrangement order of the external protrusions To even the outer bumps. In other words, the corresponding relationship between the connection points of the outer pins and the outer protrusions is not equal to the corresponding relationship between the spatial arrangement. If clearly defined, the joints of the external pins are arranged according to a "corresponding sequence of protrusions", which represents the corresponding relationship between the joints of the external pins and the joints of the external protrusions in connection with each other, and the joints of the external protrusions The blocks are arranged according to a "arranging order of the outer protrusions", and the corres...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com