Semiconductor device manufacturing method

A manufacturing method and semiconductor technology, applied in the fields of semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of time-consuming and complicated processes, and achieve the effect of reducing the amplitude.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

[0059] 1. Method of Manufacturing a Semiconductor Device in Embodiment 1

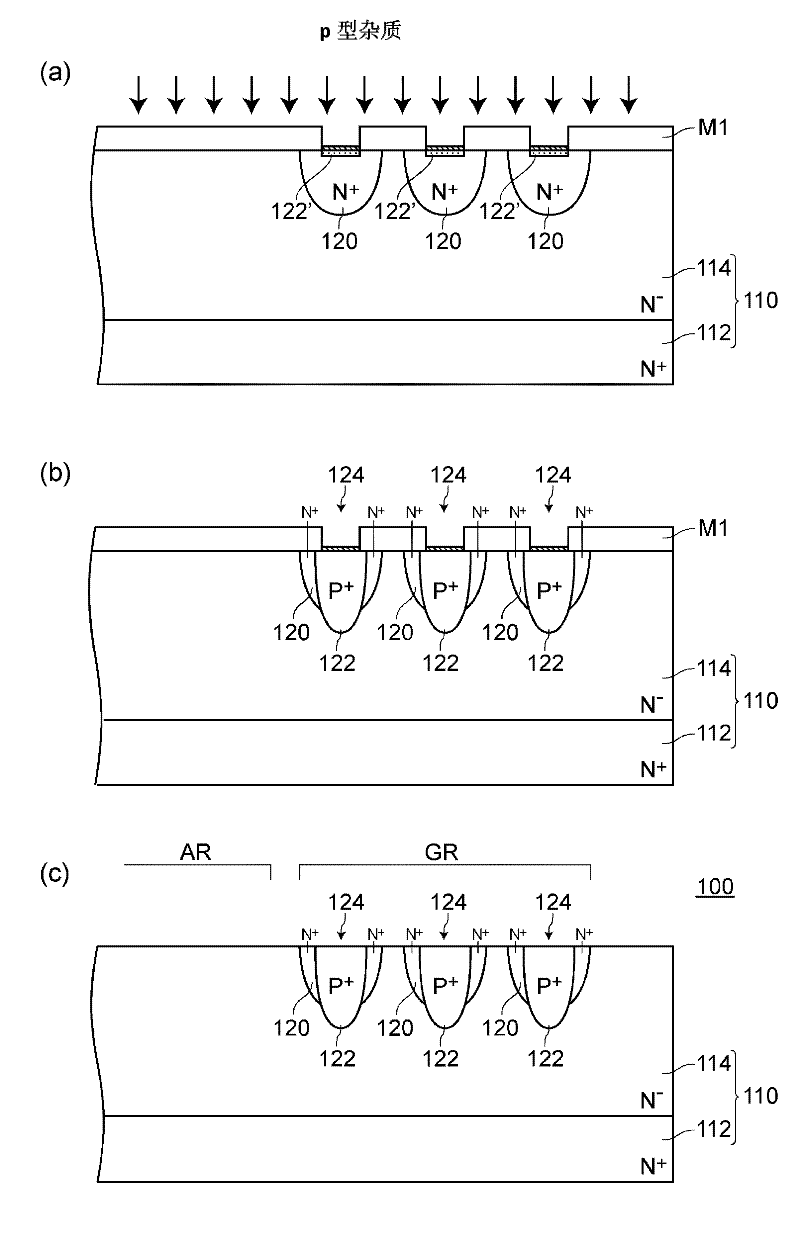

[0060] figure 1 and figure 2 It is an explanatory diagram showing the manufacturing method of the semiconductor device according to the first embodiment. figure 1 (a)~ figure 1 (c) and figure 2 (a)~ figure 2 (c) is each process drawing. In addition, in figure 1 In (b), symbol 120' represents an n-type impurity introduction region, where figure 1 (c), symbol 121 represents the oxide film, in figure 2 In (a), reference numeral 122' denotes a p-type impurity-introduced region.

[0061] Such as figure 1 and figure 2 As shown, the manufacturing method of the semiconductor device in Embodiment 1 has a plurality of MOSFETs (not shown in the figure) formed in the active region AR of the semiconductor substrate 110 and a plurality of guards 124 formed in the guard ring region surrounding the active region AR. The manufacturing method of the semiconductor device 100 includes the following steps ...

Embodiment approach 2

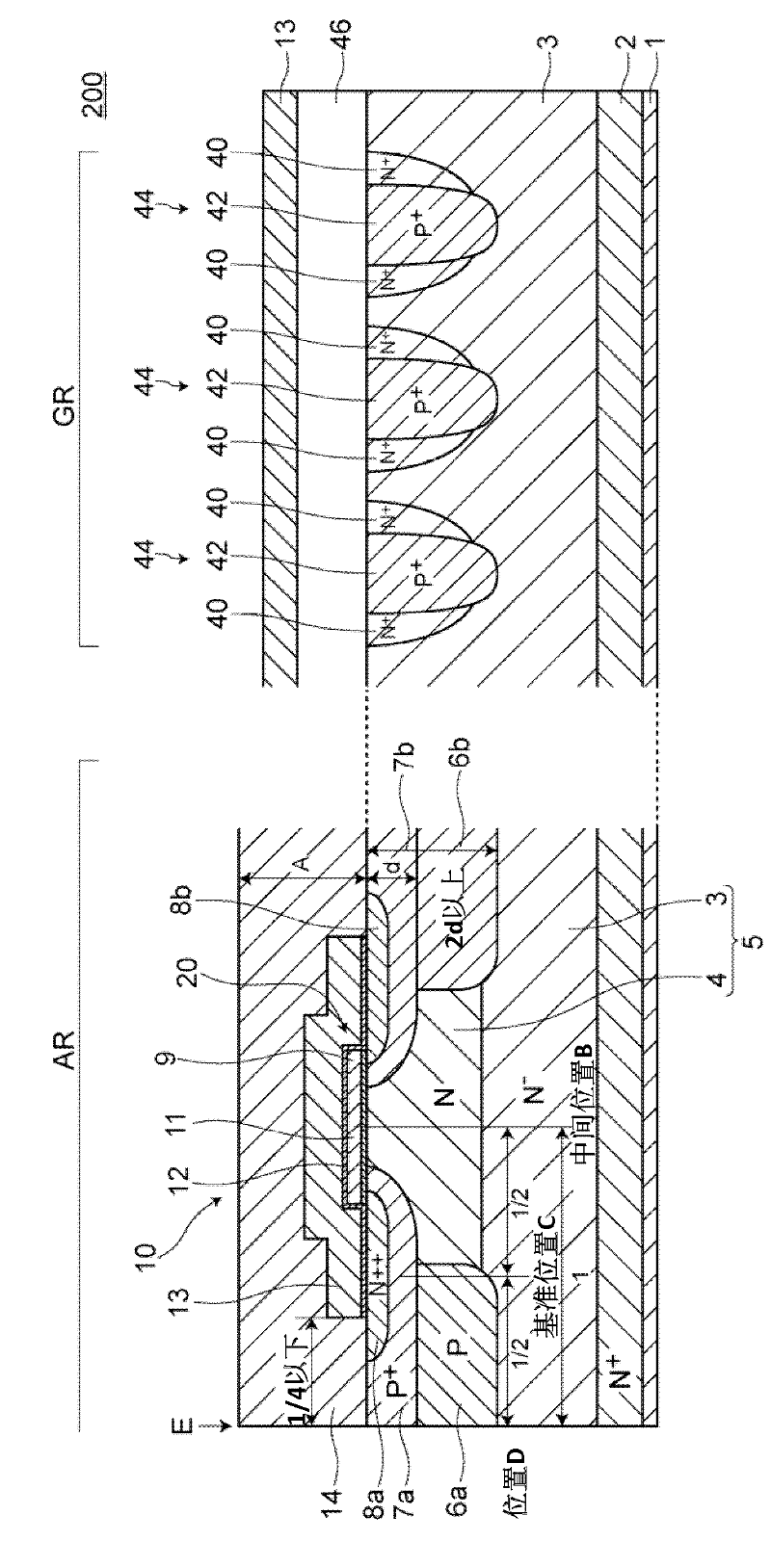

[0079] 1. Structure of semiconductor device 200

[0080] image 3 It is a cross-sectional view of the semiconductor device 200 of the second embodiment.

[0081] Such as image 3 As shown, the semiconductor device 200 of Embodiment 2 has a plurality of MOSFETs (field effect transistors) 10 formed on the active region AR and a plurality (in this case, three rows) of guard rings 44 formed on the guard region GR.

[0082] Such as image 3 As shown in FIG. The drift layer 5, and the gate electrode structure 20 formed on the surface of the reference concentration layer 4. In addition, near the surface of the reference concentration layer 4 where the gate electrode structure 20 is formed, and on the surface of the semiconductor substrate near the opposite end of the gate electrode structure 20 with a predetermined distance, a pair of diffusers are respectively provided. regions, that is, source regions (first conductivity type semiconductor regions) 8a and 8b containing n-typ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com