Erasing voltage rise control circuit of flash memory

An erasing voltage and control circuit technology, applied in the field of erasing voltage rising control circuits, can solve the problems of inaccurate erasing voltage rising time, the circuit cannot be executed accurately and quickly, and achieve the effect of accurate erasing voltage rising time

Active Publication Date: 2011-06-15

SHANGHAI HUAHONG GRACE SEMICON MFG CORP

View PDF3 Cites 11 Cited by

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

In order to overcome the problem that the erasing voltage rise time of the flash memory erasing voltage rise control circuit in the prior art is inaccurate, resulting in the inability to perform accurate and quick subsequent circuit processing, the main purpose of the present invention is to provide a flash memory erasing voltage The rise control circuit, through the negative feedback of the system and the reference current and charging current generated by the supply voltage, avoids the extra current load on the high voltage output of the charge pump, so that the rise time of the erasing voltage is more accurate

Method used

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

View moreImage

Smart Image Click on the blue labels to locate them in the text.

Smart ImageViewing Examples

Examples

Experimental program

Comparison scheme

Effect test

Embodiment Construction

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More PUM

Login to View More

Login to View More Abstract

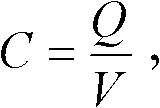

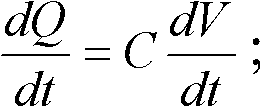

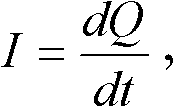

The invention discloses an erasing voltage rise control circuit of a flash memory, at least comprising a charge pump, a sampling circuit, a controllable-duty-cycle pulse generating circuit, a reference voltage generating circuit, a first capacitor and a comparison circuit, wherein the charge pump is used for generating an erasing voltage; the sampling circuit is used for sampling the erasing voltage; the controllable-duty-cycle pulse generating circuit is used for generating a pulse with a controllable duty-cycle; the reference voltage generating circuit is connected with a power supply voltage and the controllable-duty-cycle pulse generating circuit so as to generate a reference voltage under the control of the controllable-duty-cycle pulse generating circuit; the first capacitor is connected between the reference voltage generating circuit and the ground; and the comparison circuit is used for comparing a sampling voltage with the reference voltage so as to generate a feedback signal to the charge pump. In the invention, because reference current and charging current are not generated by virtue of high-voltage output of the charge pump, extra current loads can not be generated to the output of the charge pump, no voltage loss is generated, and the rise time of the erasing voltage is more accurate.

Description

Flash memory erase voltage rise control circuit technical field The present invention relates to an erasing voltage rise control circuit, in particular to a flash memory erasing voltage rise control circuit. Background technique In a flash memory, especially a low-voltage flash memory device, it is often necessary to generate an erasing voltage through a charge pump (ChargePump). Since the erasing voltage generated by the charge pump without any restrictions often deviates from the required value, in the prior art flash memory, a control circuit is usually set to control the erasing voltage output by the charge pump. Fig. 1 is a circuit structure diagram of an erasing voltage control circuit of a flash memory in the prior art, as shown in Fig. 1, the control circuit includes a charge pump 11, a pulse generation circuit 12 with a controllable duty ratio, a PMOS transistor P1, The mirror constant current source 13, capacitor C and NMOS transistor N2 formed by P2 and NMOS t...

Claims

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More Application Information

Patent Timeline

Login to View More

Login to View More Patent Type & Authority Applications(China)

IPC IPC(8): G11C16/06G11C16/14

Inventor 杨光军

Owner SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Features

- Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com