Offset voltage elimination technology for differential time domain comparator

A time-domain comparator, offset voltage technology, applied in multiple input and output pulse circuits, instruments, electrical components, etc., can solve problems that affect the performance of high-precision successive approximation analog-to-digital converters and cannot be completely eliminated.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0048] The present invention will be described in further detail below in conjunction with the accompanying drawings.

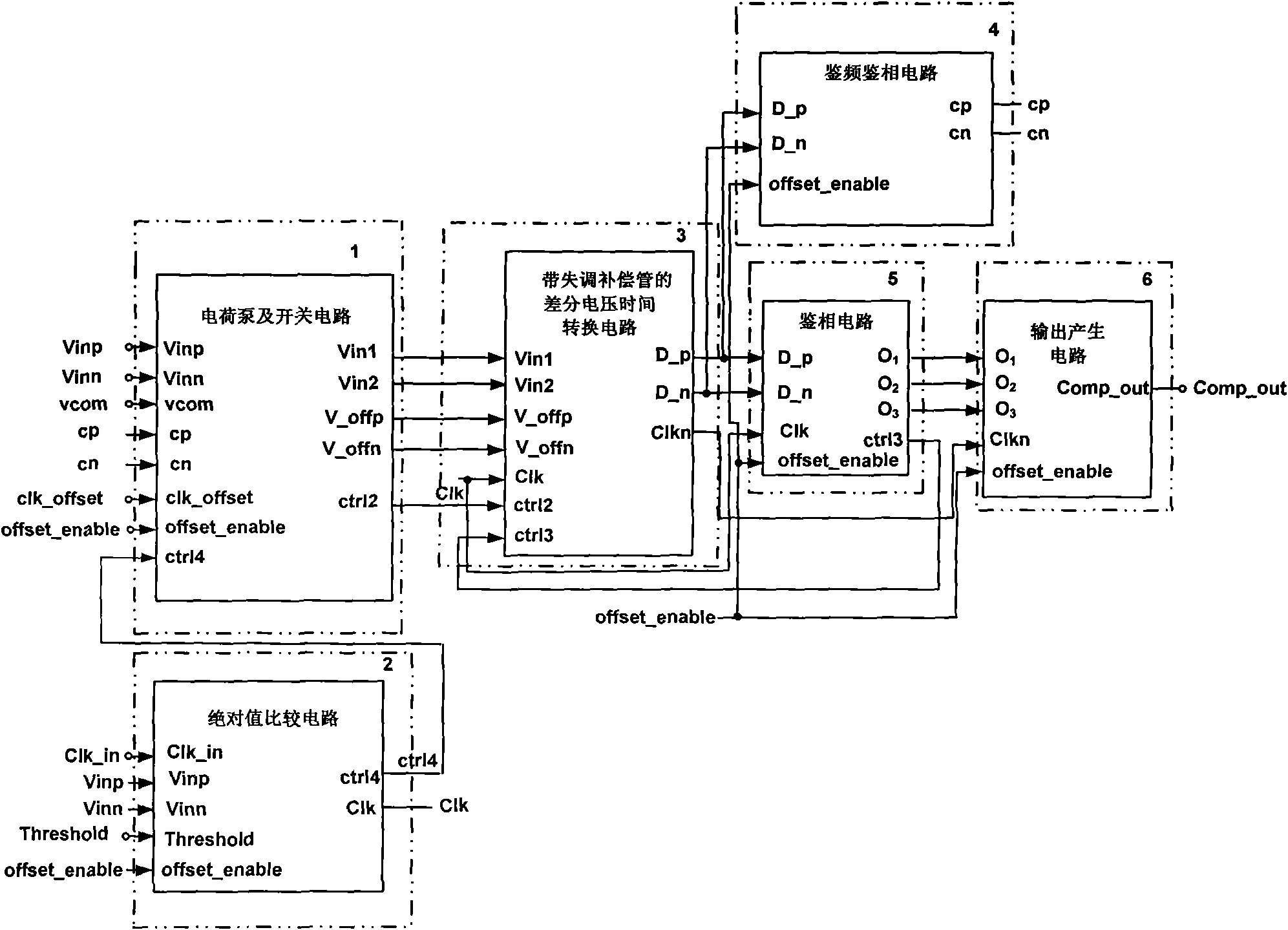

[0049] figure 1 Shown is a system structure diagram of an offset voltage elimination technology that can be used in a differential time domain comparator circuit provided by the present invention, including a charge pump and a switch circuit (1), an absolute value comparison circuit (2), and an offset compensation tube A differential voltage time conversion circuit (3), a frequency and phase detection circuit (4), a phase detection circuit (5) and an output generation circuit (6).

[0050] figure 2 It is a schematic diagram of the timing relationship of some digital signals in the present invention. During offset_enable equal to 1, figure 1 The circuit shown works in the state of offset cancellation, and when offset_enable is equal to 0, figure 1 The circuit shown works in a comparative working state.

[0051] image 3 It is the circuit diagram of the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com