Chip and manufacturing method thereof

A chip and lining technology, applied in the field of chip and its manufacturing, can solve problems such as damage and impact on chip yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

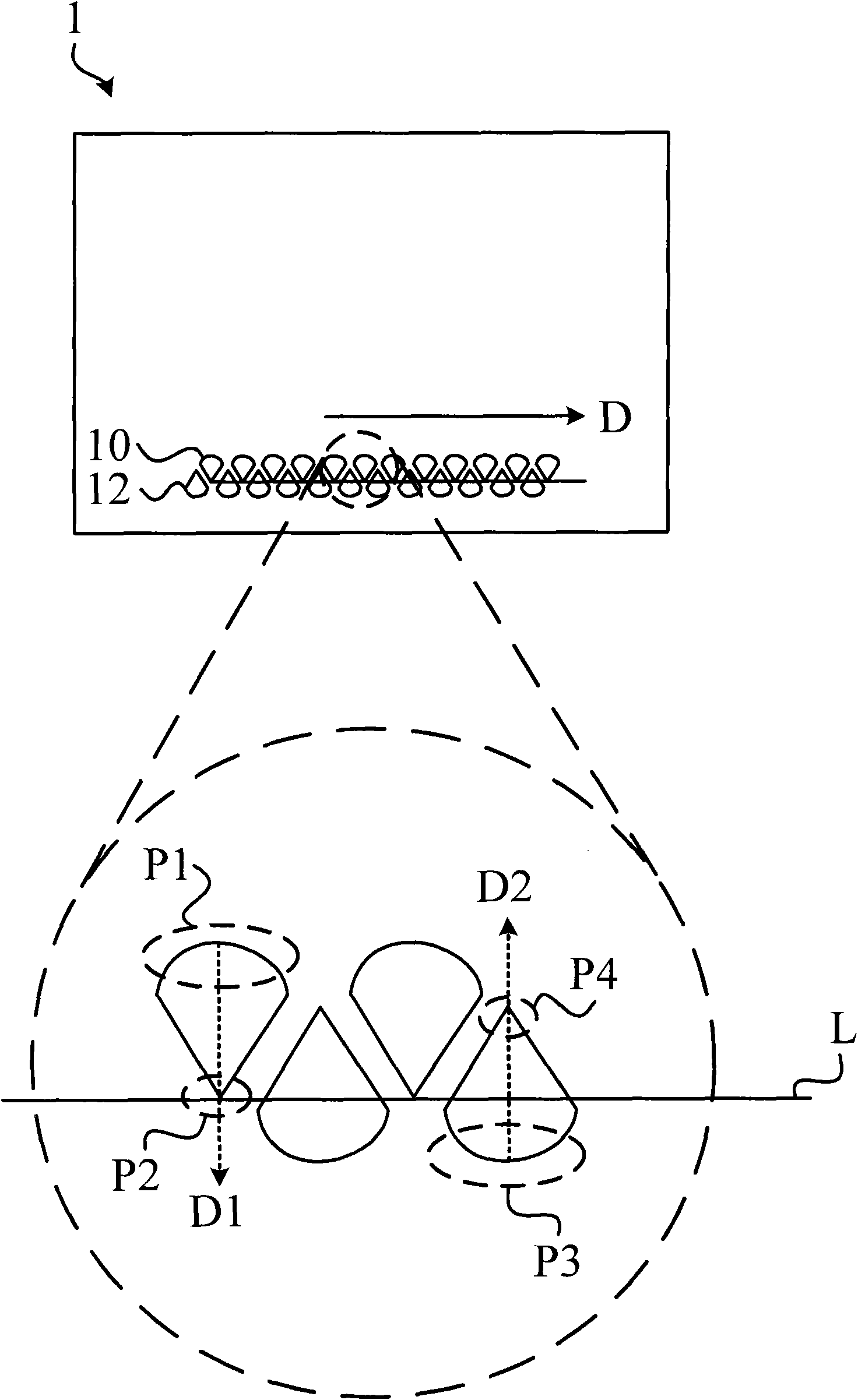

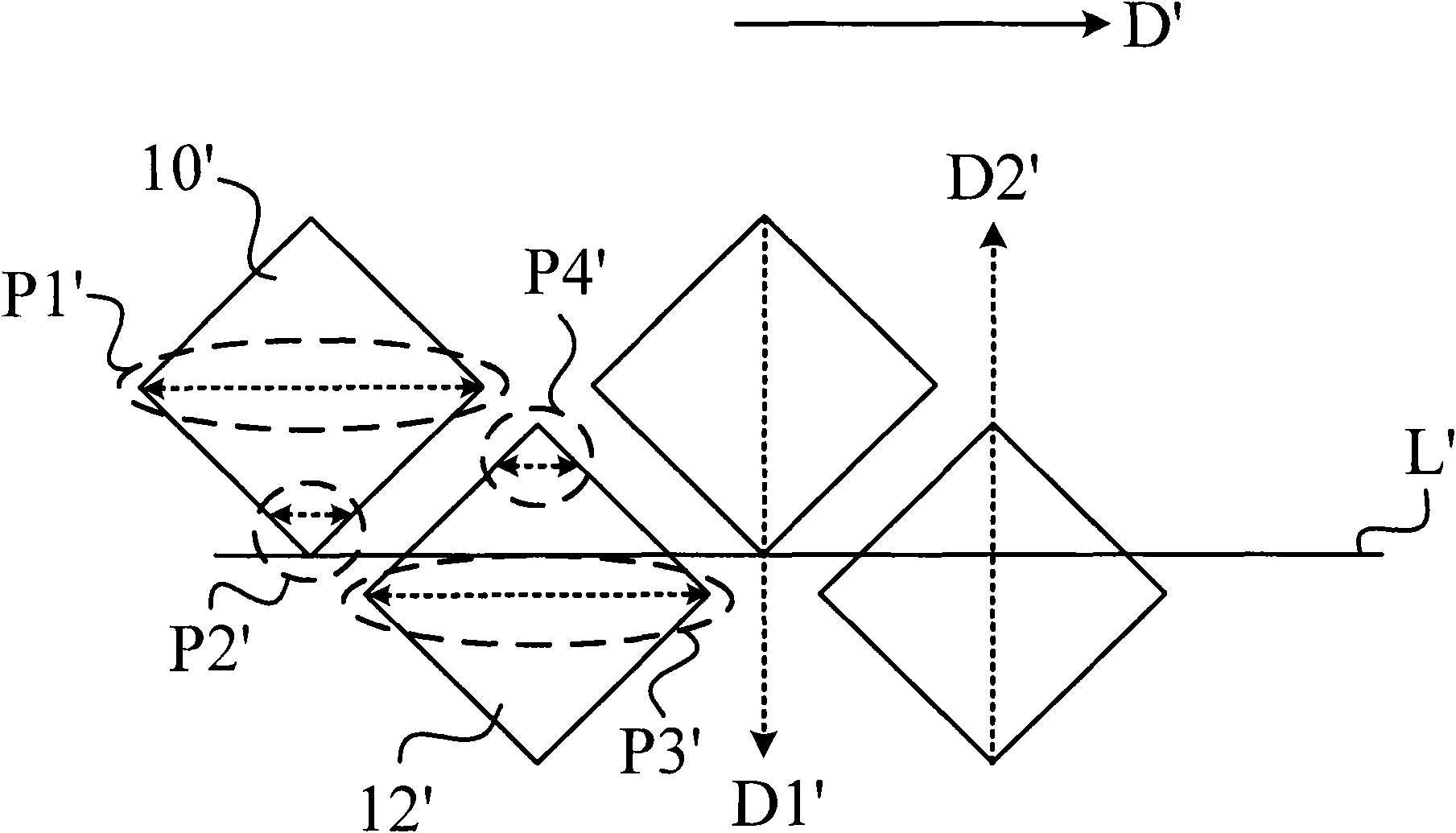

[0047] see Figure 2A , Figure 2A is a schematic diagram of a chip 1 according to a specific embodiment of the present invention. Such as Figure 2A As shown, the chip 1 includes a plurality of first conductive pads 10 and a plurality of second conductive pads 12 approximately in the shape of water droplets. The first conductive linings 10 and the second conductive linings 12 are arranged alternately in a predetermined direction D, respectively. Each first conductive lining 10 includes a first portion P1 and a second portion P2 corresponding to the first portion P1 , and the length of the first portion P1 along the predetermined direction D is greater than the length of the second portion P2 along the predetermined direction D. Each second conductive lining 12 includes a third portion P3 and a fourth portion P4 relative to the third portion P3, and the length of the third portion P3 along the predetermined direction D is greater than that of the fourth portion P4 along the p...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com