Method for processing address discontinuity in MTD design of NAND flash memory

A technology of flash memory and address, which is applied in MTD design to deal with discontinuous addresses, and can solve problems such as NAND flash memory that cannot be adapted and does not support multi-planes

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

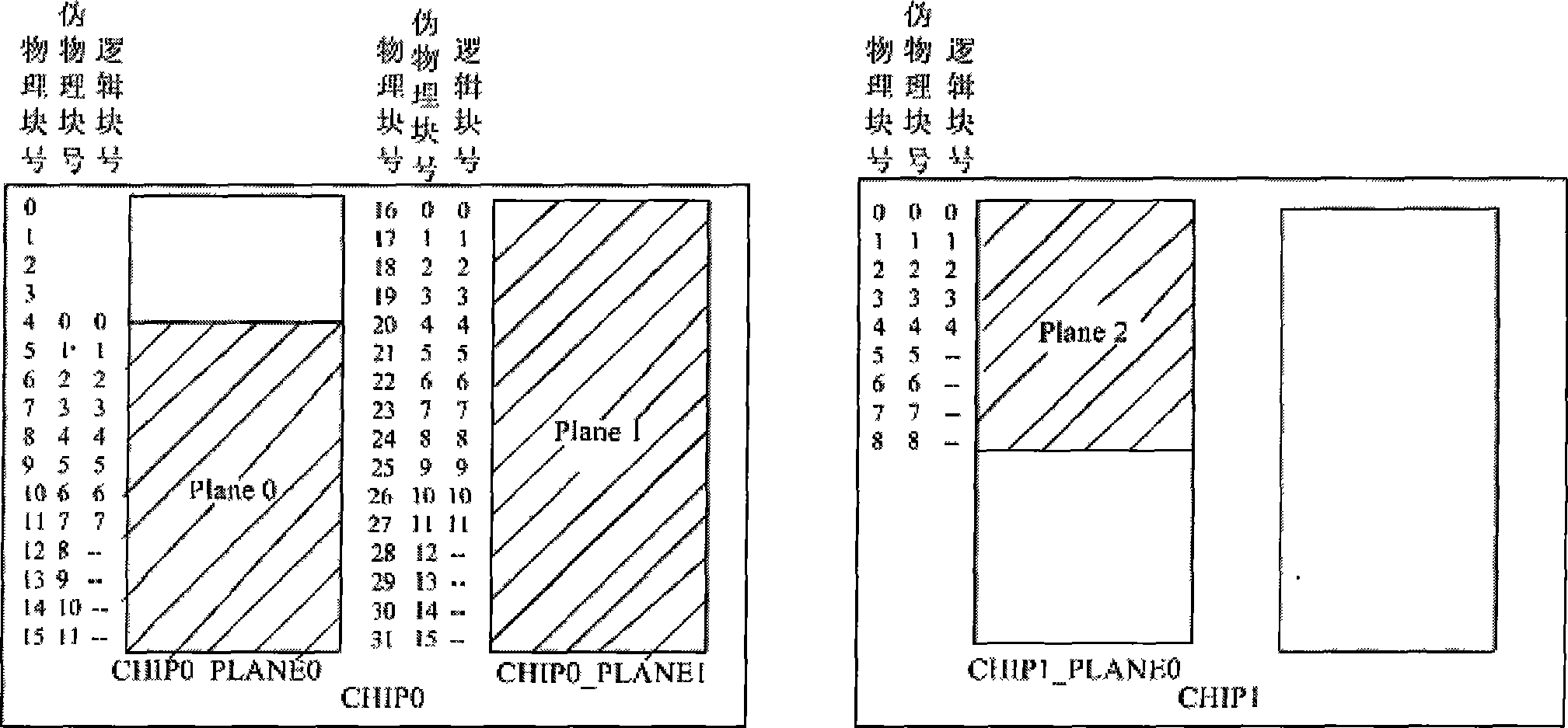

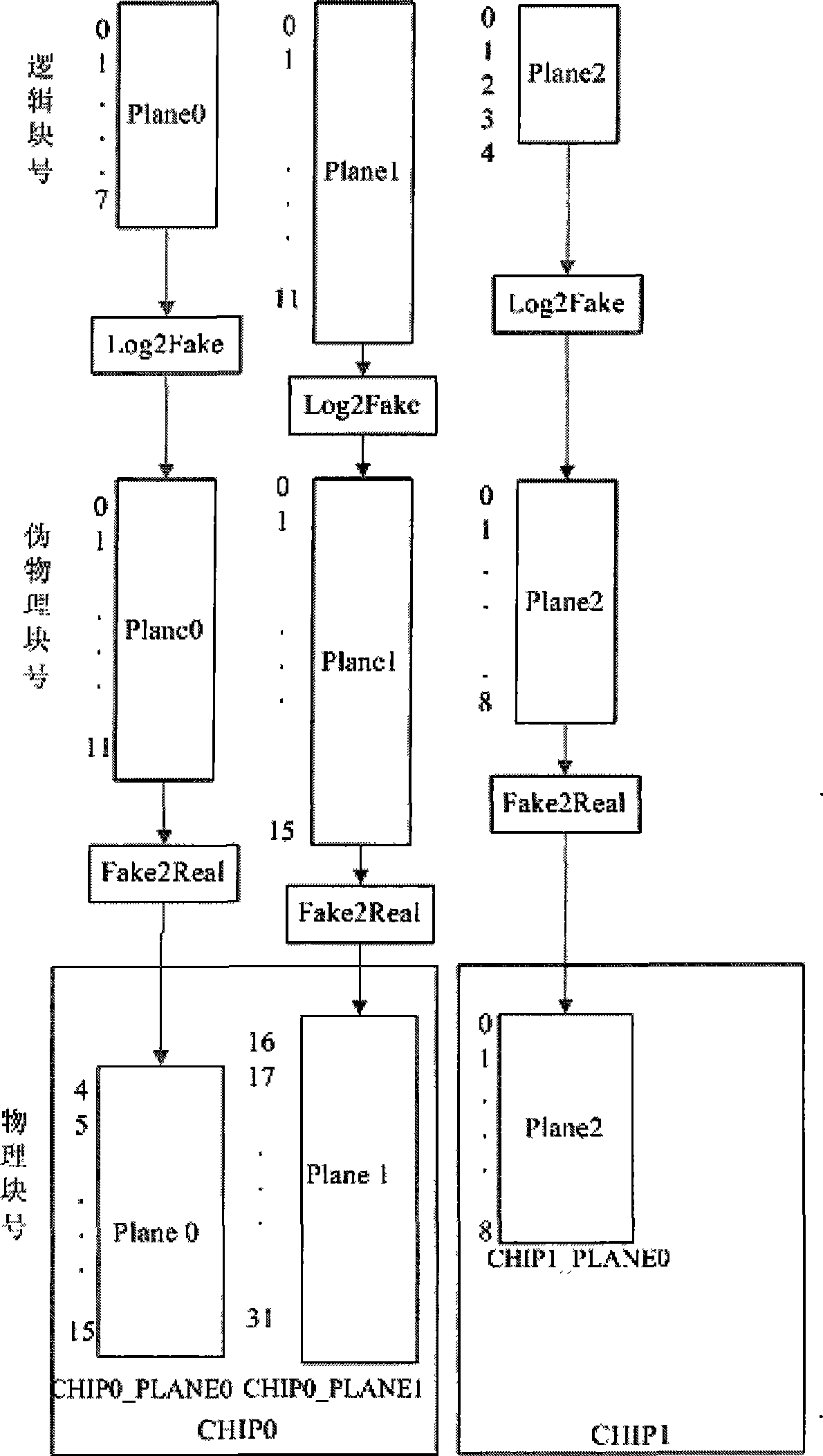

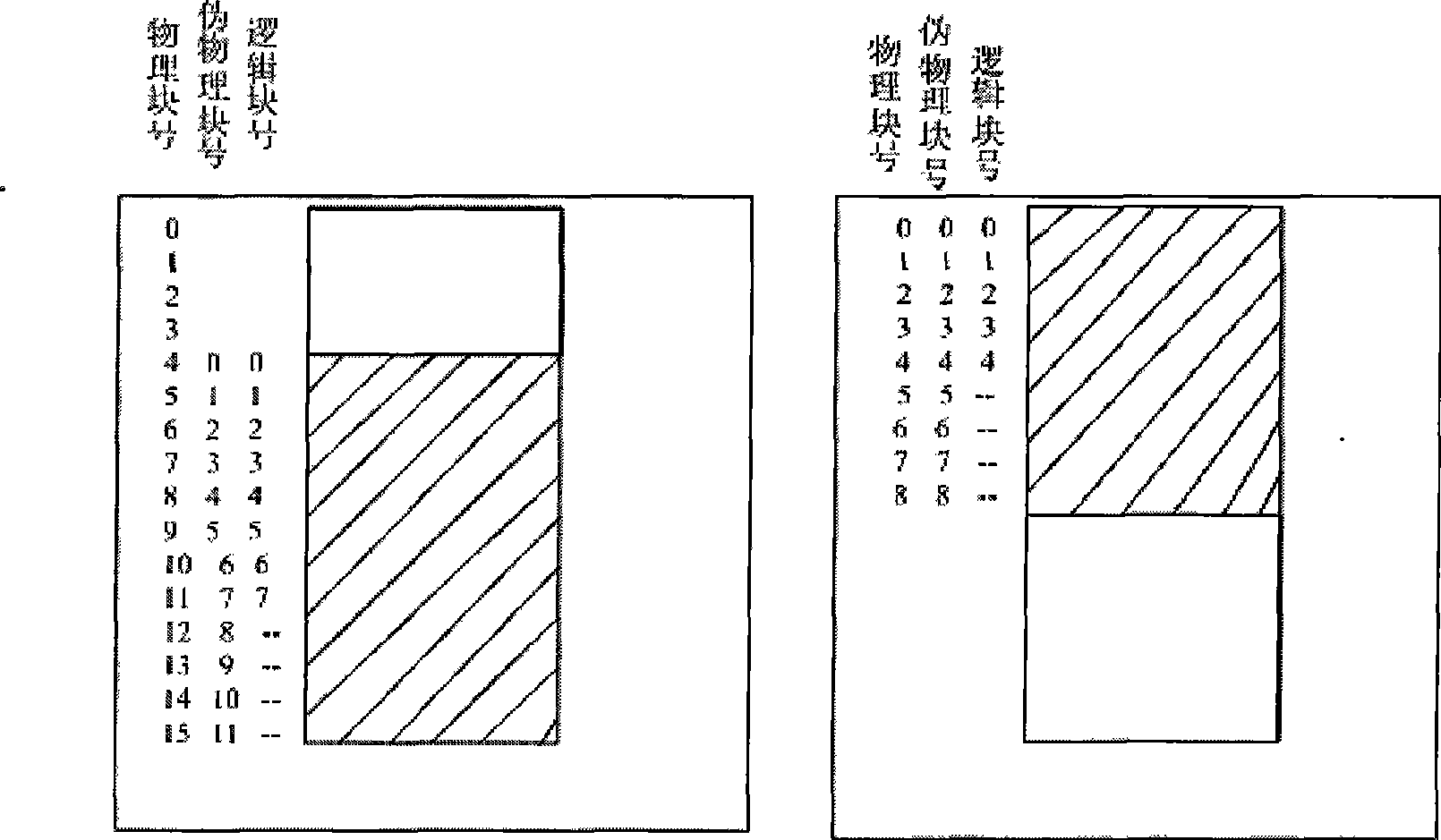

[0019] 1. According to the specific requirements of upper-layer applications such as storage content security requirements, the entire NAND flash memory space is divided into several different areas. One area may span multiple physical planes, or even multiple NAND flash memory chips. Each such divided area is managed by an MTD. The MTD needs to record the number of the physical plane where the first physical block of its management area is located and the offset of the physical block relative to the physical plane. figure 1 It is the division of two NAND flash memory chips, the front and rear addresses are divided into two physical planes, and the three logical planes Plane0, Plane1 and Plane2 are the area to be governed by an MTD. The three columns of numbers on the left side of the area are from left to right as shown in the figure, respectively representing the physical block number, pseudo-physical block number and logical block number. Each column of numbers is limited t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com