Integrated circuit diagram optimizing method based on mathematical morphologic

A mathematical morphology and integrated circuit technology, applied in the field of microelectronics, can solve problems such as inaccurate layout optimization design

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

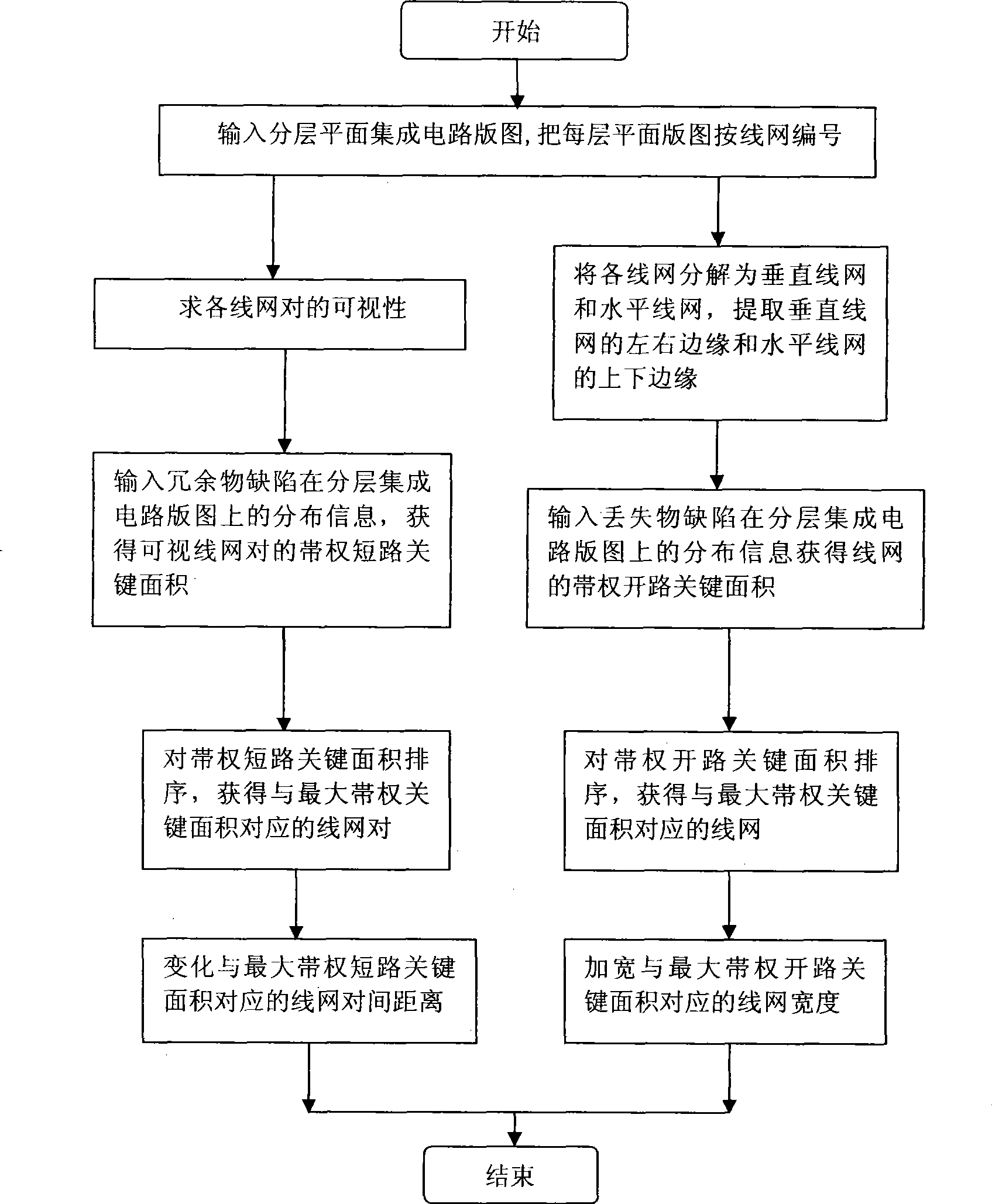

[0067] refer to figure 1 The layout optimization method implemented in the present invention is to characterize the defect parameters on the basis of the collected defect characteristic parameters related to the integrated circuit technology of each layer, and then optimize the plane layout of different process layers according to the plane layout of the input integrated circuit chip . Defect characteristic parameters related to each layer process generally include defect shape, defect particle size distribution, and defect spatial distribution characteristics. In the embodiment of the present invention, the layout of the integrated circuit can be intuitively optimized according to the analyzed defect data, and the specific process is as follows:

[0068] In the first step, the planar layout of each layer of the integrated circuit to be estimated is numbered according to the net.

[0069] First, the layout is decoded to form a two-color multi-layer planar layout; then, each ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com