Method and subassembly for testing two-sided chip photoelectric performance

A technology for photoelectric performance and testing components, which is applied in the direction of testing optical performance, measuring electricity, and measuring electrical variables, etc. It can solve problems such as inaccurate easy bonding, chip damage, and chip electrode damage, and achieve the effect of ensuring repeatability and accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

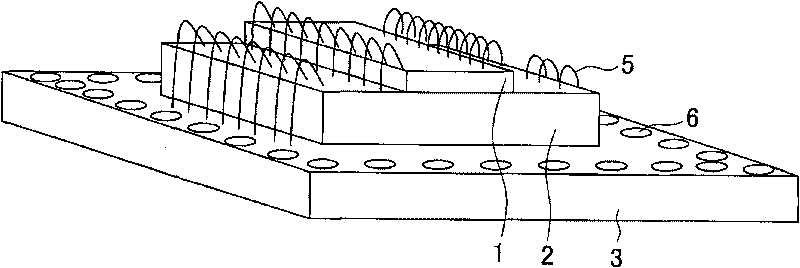

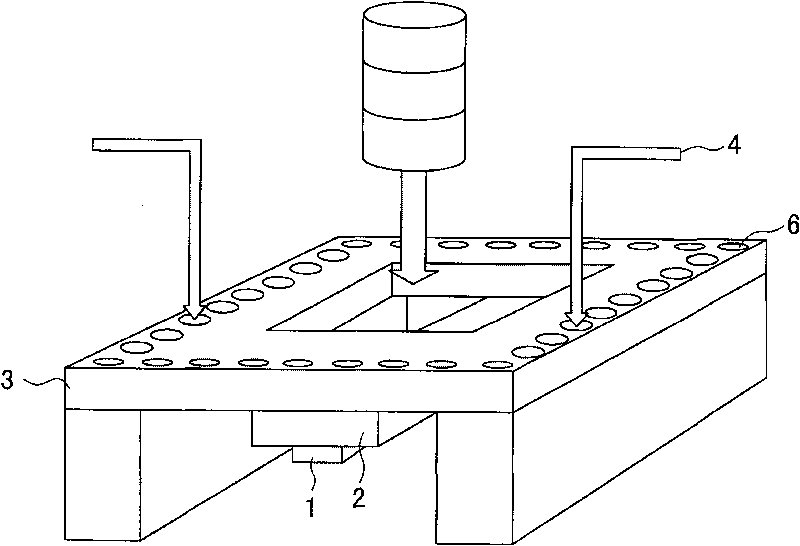

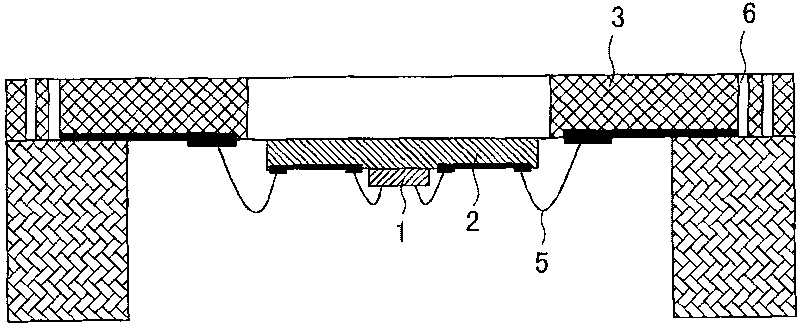

[0032] Embodiment one, see appendix Figure 1~4 Shown:

[0033] A method for testing the photoelectric performance of a double-sided chip, comprising the following steps:

[0034] (1) Build a test assembly, the test assembly includes a printed circuit board 3 that is provided with a lead-out circuit corresponding to the electrode of the double-sided chip 1 to be tested, and the light-receiving position of the printed circuit board 3 is corresponding to the double-sided chip 1 to be tested. Each electrode of the double-sided chip 1 to be tested is electrically connected to the corresponding lead-out circuit on the printed circuit board 3 through a gold wire 5 connection, and a test electrode 6 is arranged at the end of each lead-out circuit;

[0035] (2) above-mentioned test assembly is placed on the test frame, and the test light is irradiated on the light-receiving position of the double-sided chip to be tested through the hole on the printed circuit board; each probe 4 is a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com