Non-volatile memory device and method of handling a datum read from a memory cell

A non-volatile memory technology, applied in static memory, read-only memory, digital memory information, etc., can solve the problem of high power consumption of memory devices

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

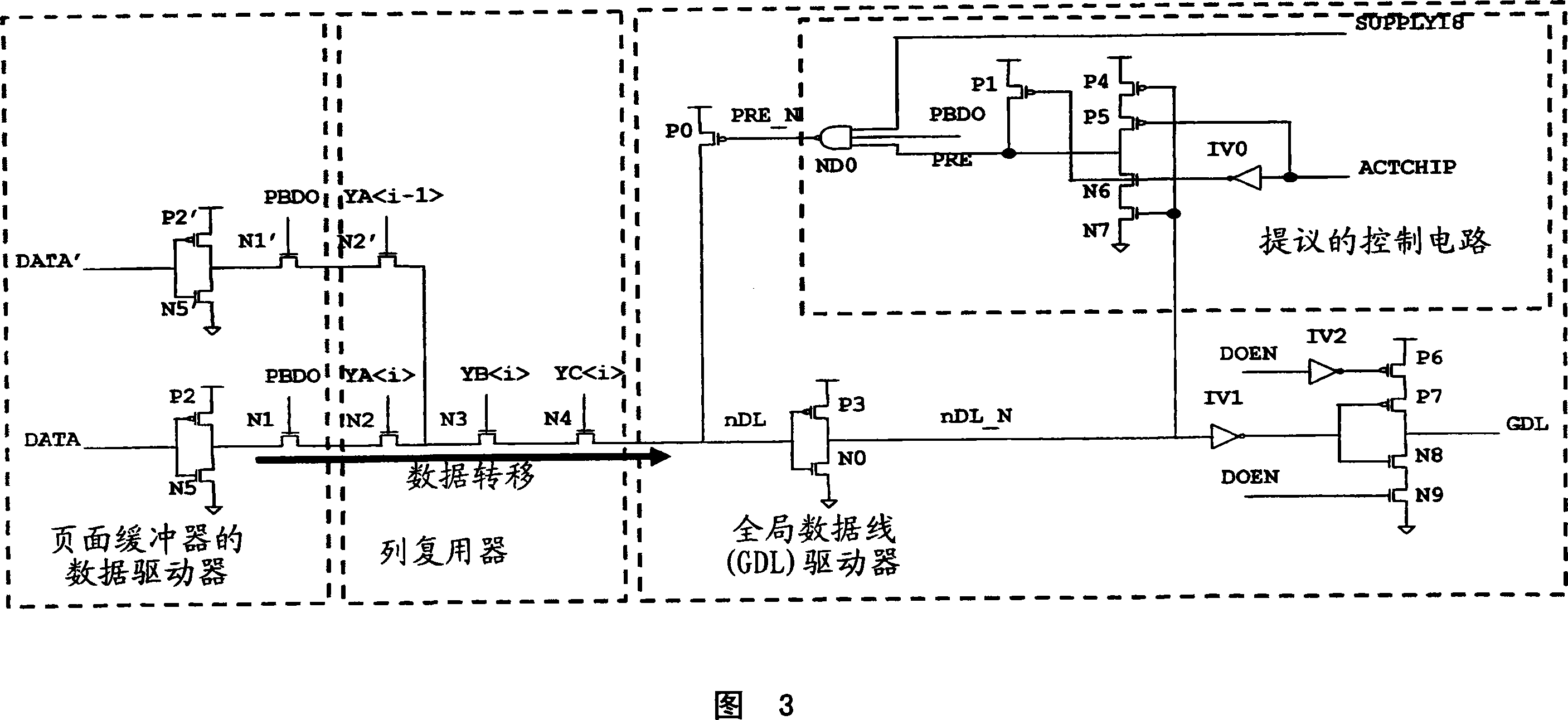

[0019] Fig. 3 shows a preferred embodiment of the global data line driver of the memory device of the present invention. Unlike the circuit shown in Figure 2, this novel global data line driver has a precharge control circuit that generates a control signal PRE_N such that the global The precharge transistor P0 is turned on only when the input line of the data line driver is precharged.

[0020] According to the method of the present invention, only when the external command SUPPLY18 is high level (that is, the memory device operates in a low voltage mode) at the same time, the enable signal PBDO is high level (that is, the page buffer is ready to output the read data) And when the internally generated auxiliary logic signal PRE is at a high level, the transistor P0 is turned on. When the standby signal ACTCHIP is high level (that is, the memory device is not in the standby state) or when the standby signal ACTCHIP is low level (that is, the memory device is in the standb...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com