Semiconductor chip mounting body and manufacturing method thereof

A technology of chip mounting and manufacturing method, applied in the direction of semiconductor/solid-state device manufacturing, semiconductor device, electric solid-state device, etc. Reliability, the effect of improving productivity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] Hereinafter, embodiments of the present invention will be described in detail with reference to the drawings.

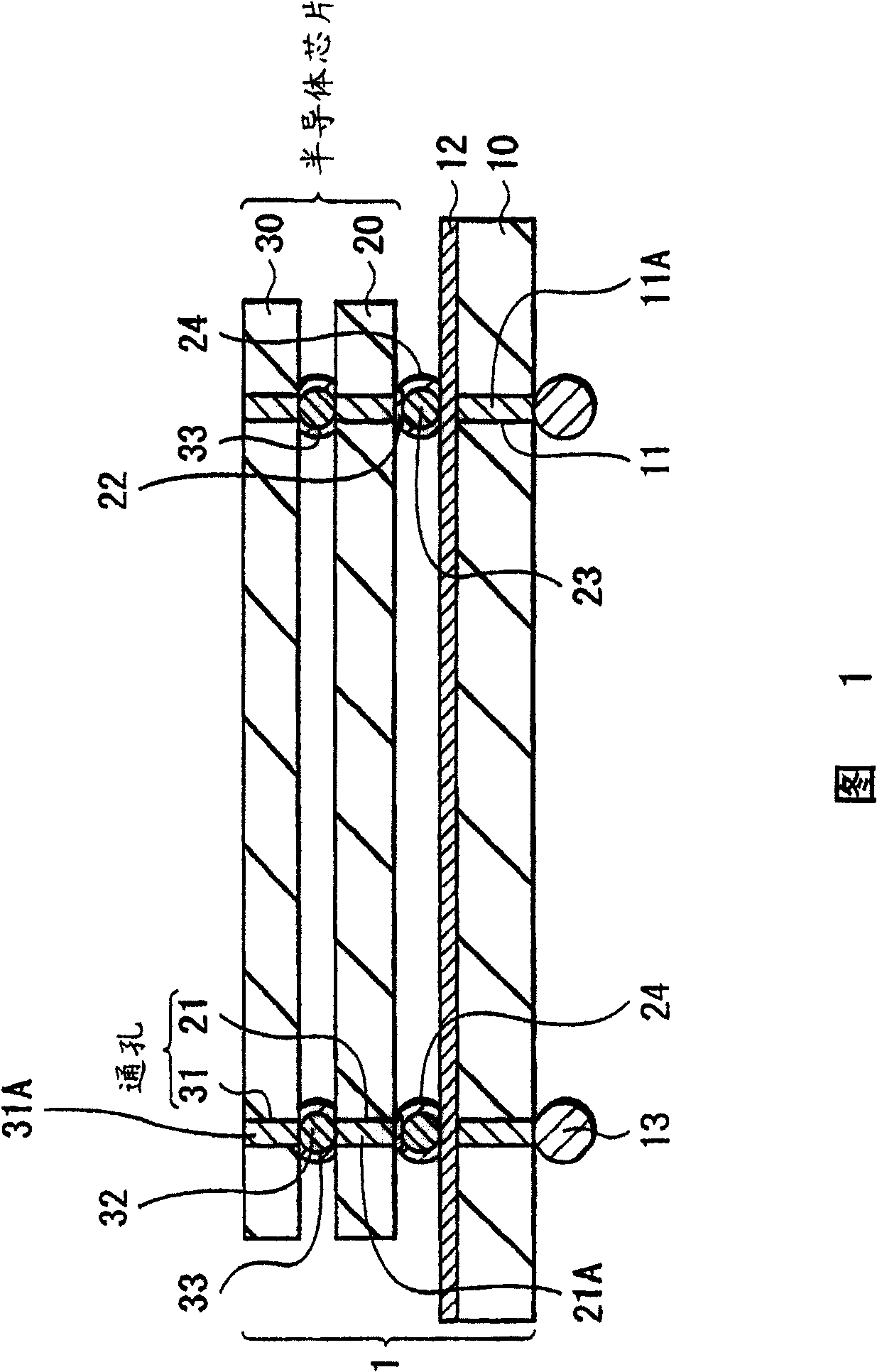

[0022] FIG. 1 is a diagram showing a cross-sectional structure of a semiconductor chip package 1 according to one embodiment of the present invention. This semiconductor chip package 1 is a package in which semiconductor chips 20 and 30 having a multilayer structure (here, two layers) are stacked and mounted on a wiring board 10 made of, for example, polyimide resin.

[0023] A through hole (electrode formation hole) 11 is provided in the wiring substrate 10, and an electronic circuit composed of a wiring layer 12 is formed on the surface. Penetrating electrodes 11A are formed on the electrode forming holes 11 . 11 A of external electrodes can be formed by electroplating nickel (Ni) of about 1-150 micrometers, for example. As another method, electrodes may be produced by remelting solder after electroplating.

[0024] Ball electrodes 13 made of, for example...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com