Three-dimensional integrated circuit structure and method of making same

a technology of integrated circuits and manufacturing methods, applied in the direction of transistors, solid-state devices, nanoinformatics, etc., can solve problems such as wide us

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

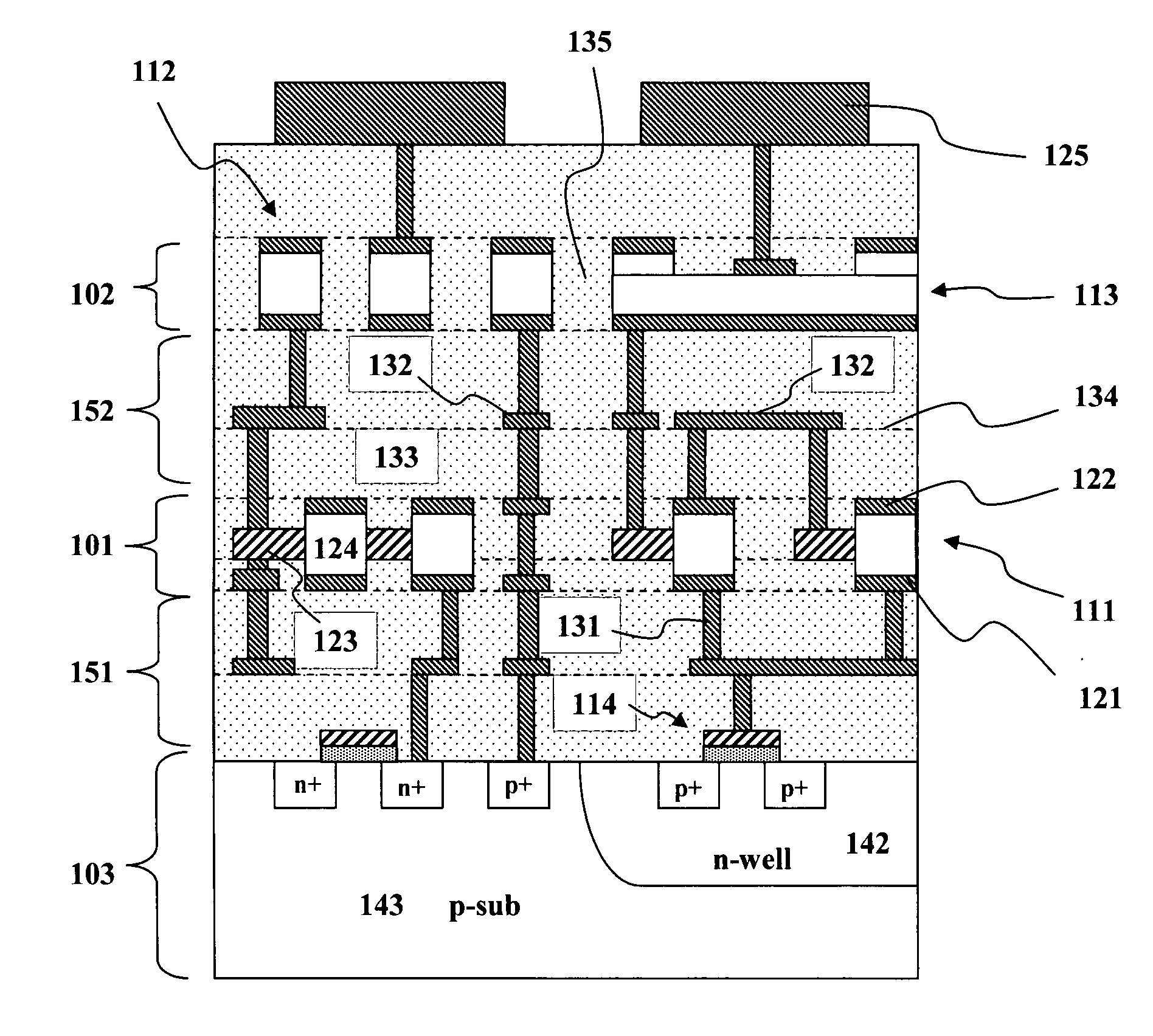

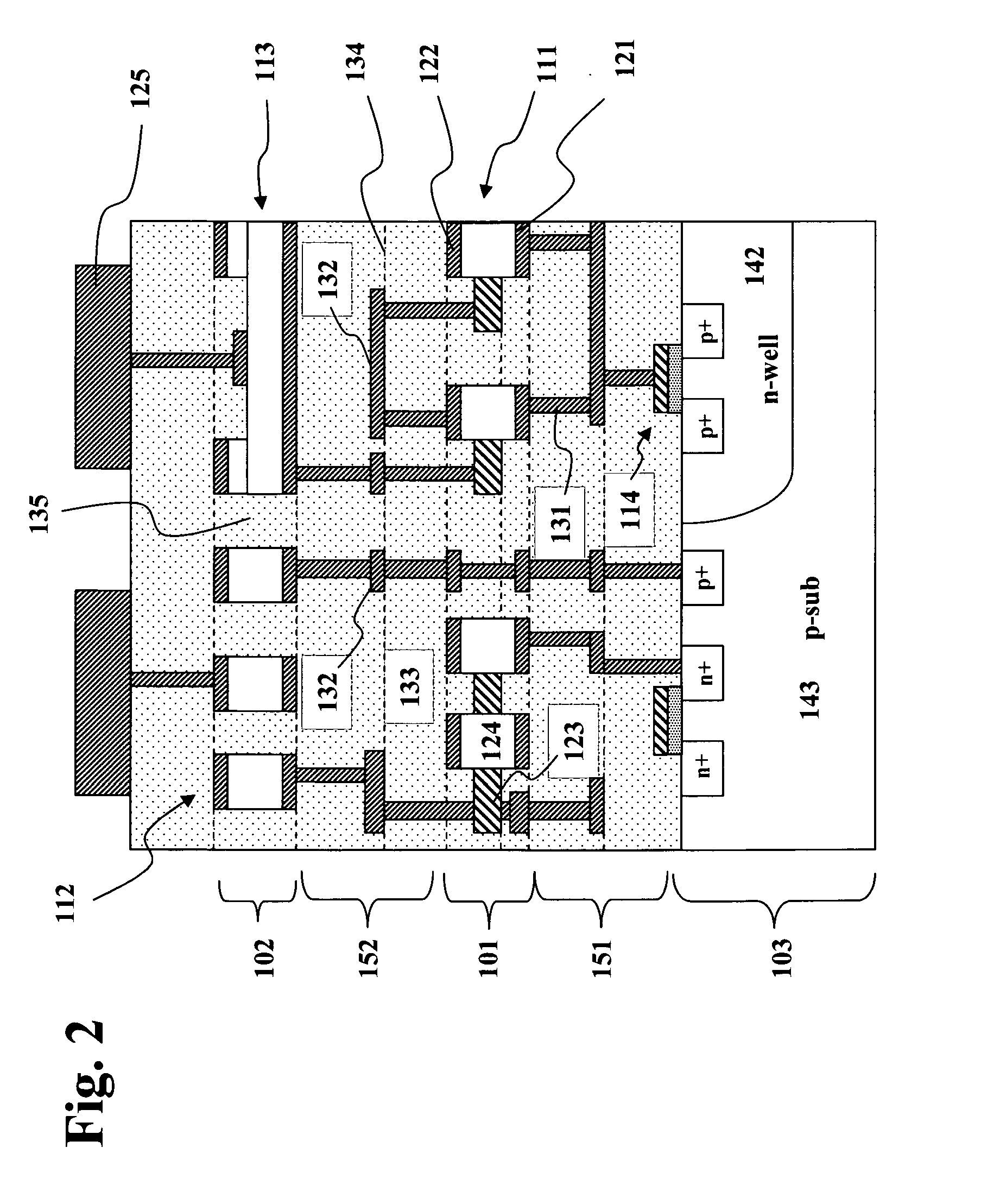

[0065] A 3-D IC in accordance with the present invention is shown in FIG. 2. Embodiments of the present invention provide a device integration technology.

[0066] Reference herein to “one embodiment”, “an embodiment”, or similar formulations, means that a particular feature, structure, operation, or characteristic described in connection with the embodiment, is included in at least one embodiment of the present invention. Thus, the appearances of such phrases or formulations herein are not necessarily all referring to the same embodiment. Furthermore, various particular features, structures, operations, or characteristics may be combined in any suitable manner in one or more embodiments.

Terminology

[0067]“ASIC” refers to Application Specific Integrated Circuit. “SoC” refers to a System on a Chip, with “SoCs” being the plural of SoC. A SoC may be an ASIC but is not required to be. An ASIC may be a SoC but is not required to be.

[0068] The expression “back bias”, as used herein, refe...

PUM

| Property | Measurement | Unit |

|---|---|---|

| temperature | aaaaa | aaaaa |

| temperatures | aaaaa | aaaaa |

| melting points | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com