Method for error handling in a converter circuit for wiring of three voltage levels

A converter circuit, voltage level technology, applied in the output power conversion device, emergency protection circuit device, irreversible DC power input into AC power output and other directions, can solve the problem of power semiconductor switch aging, damage, power semiconductor Switch burden, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

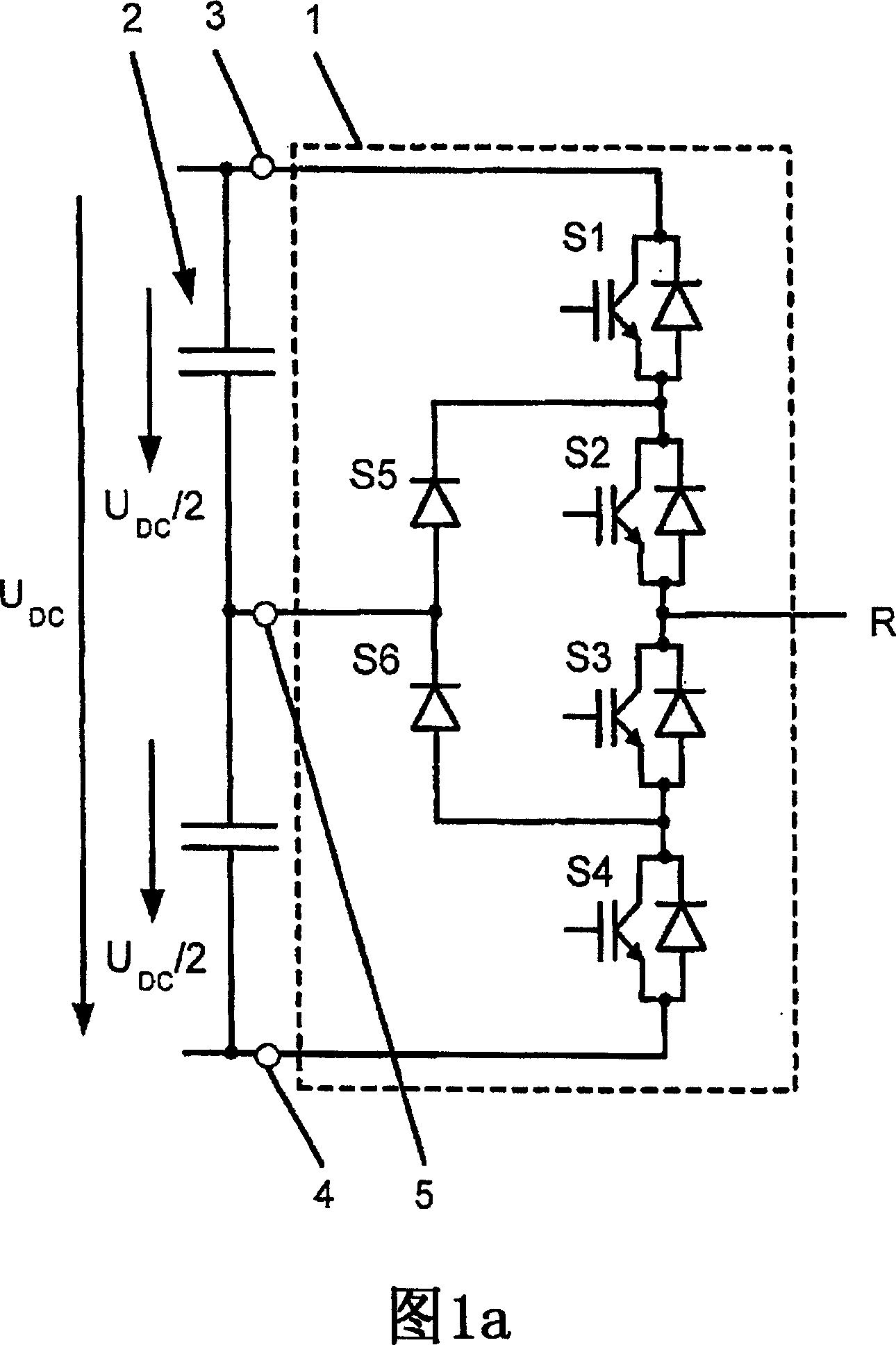

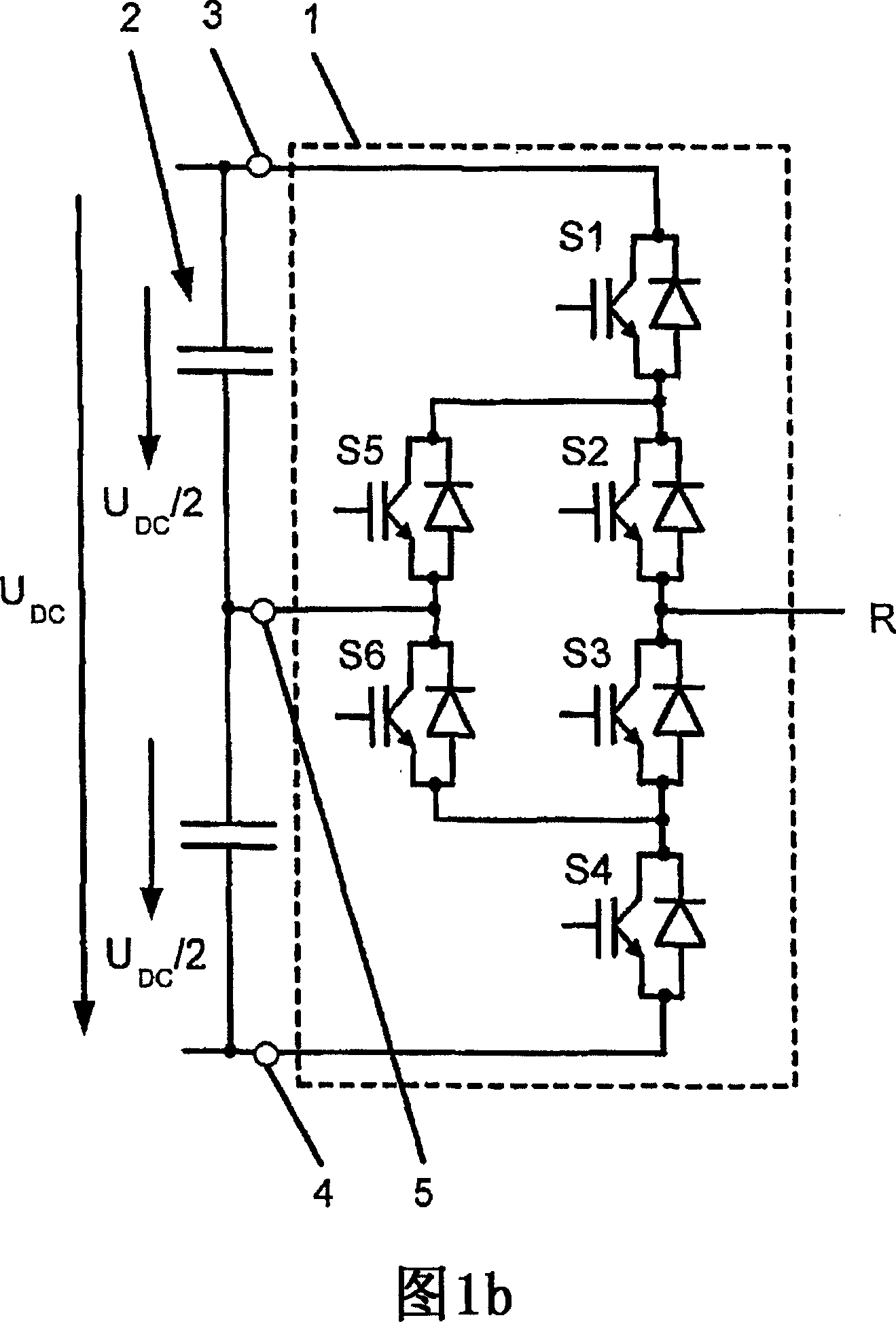

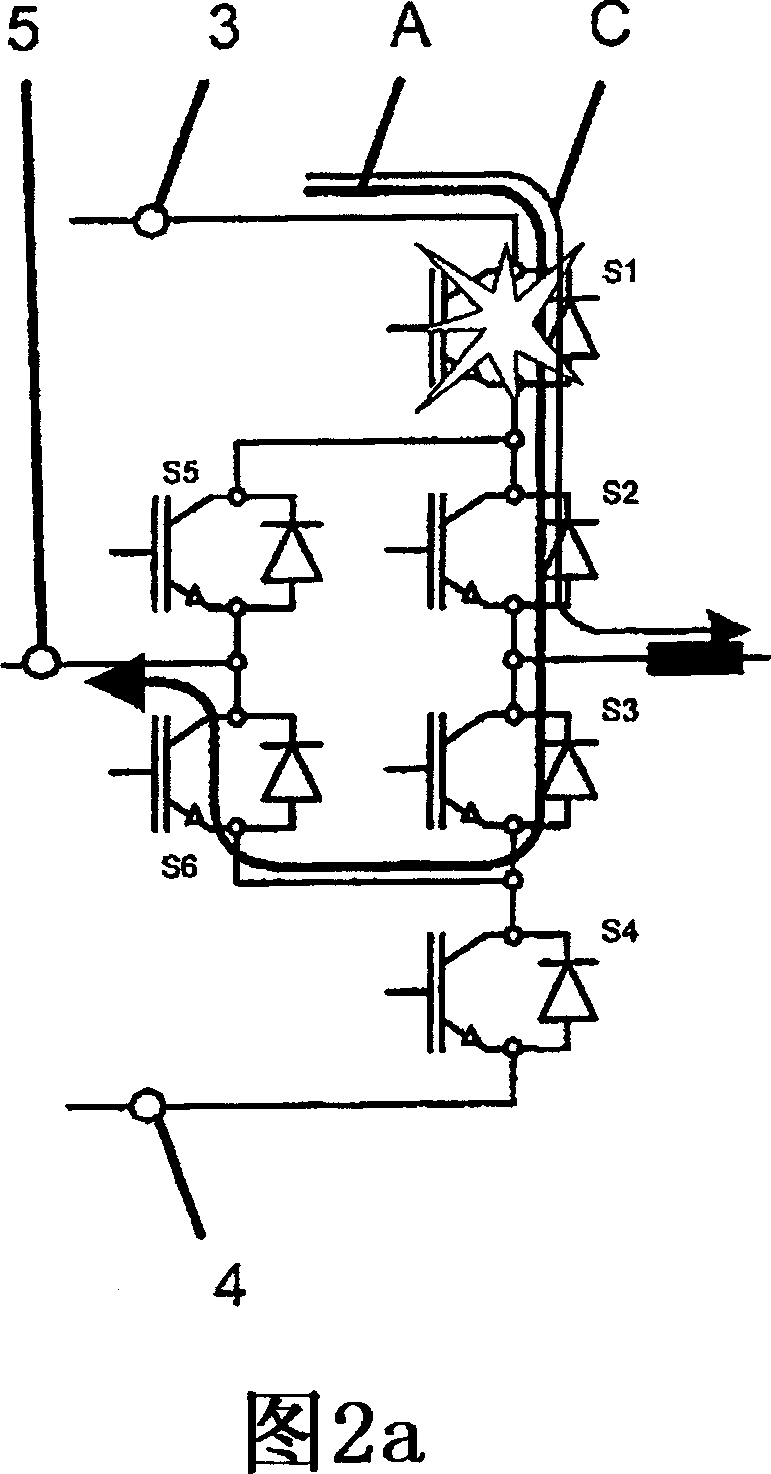

[0020]Figure 1a shows an embodiment of a known conventional converter subsystem 1 in a converter circuit for switching three voltage levels (already described in detail at the outset). The converter circuit has a converter subsystem 1 provided for each phase R, S, T, only one converter subsystem 1 for phase R is shown in FIG. 1a. The converter circuit comprises a DC voltage circuit 2 constituted by two capacitors connected in series, the first main connection 3 and the second main connection 4 and the secondary connection 5 of the DC voltage circuit 2 constituted by two adjacent and interconnected capacitors. In addition, the converter subsystem 1 has first, second, third and fourth actuatable bidirectional power semiconductor switches S1 , S2 , S3 , S4 and fifth and sixth power semiconductor switches S5 , S6 . In particular, each actuatable bidirectional power semiconductor switch S1 , S2 , S3 , S4 consists of an insulated gate bipolar transistor (IGBT) and a diode connected ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com