A three-dimensional wafer stacking structure with post-and-beam construction and method to stack three-dimensional wafer

A technology of stacked structure and wafer, applied in the direction of electrical components, electric solid devices, circuits, etc., can solve the problems of thermal stress damage, chip circuit damage, inability to support the device layer, etc., to achieve the effect of stress-free damage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

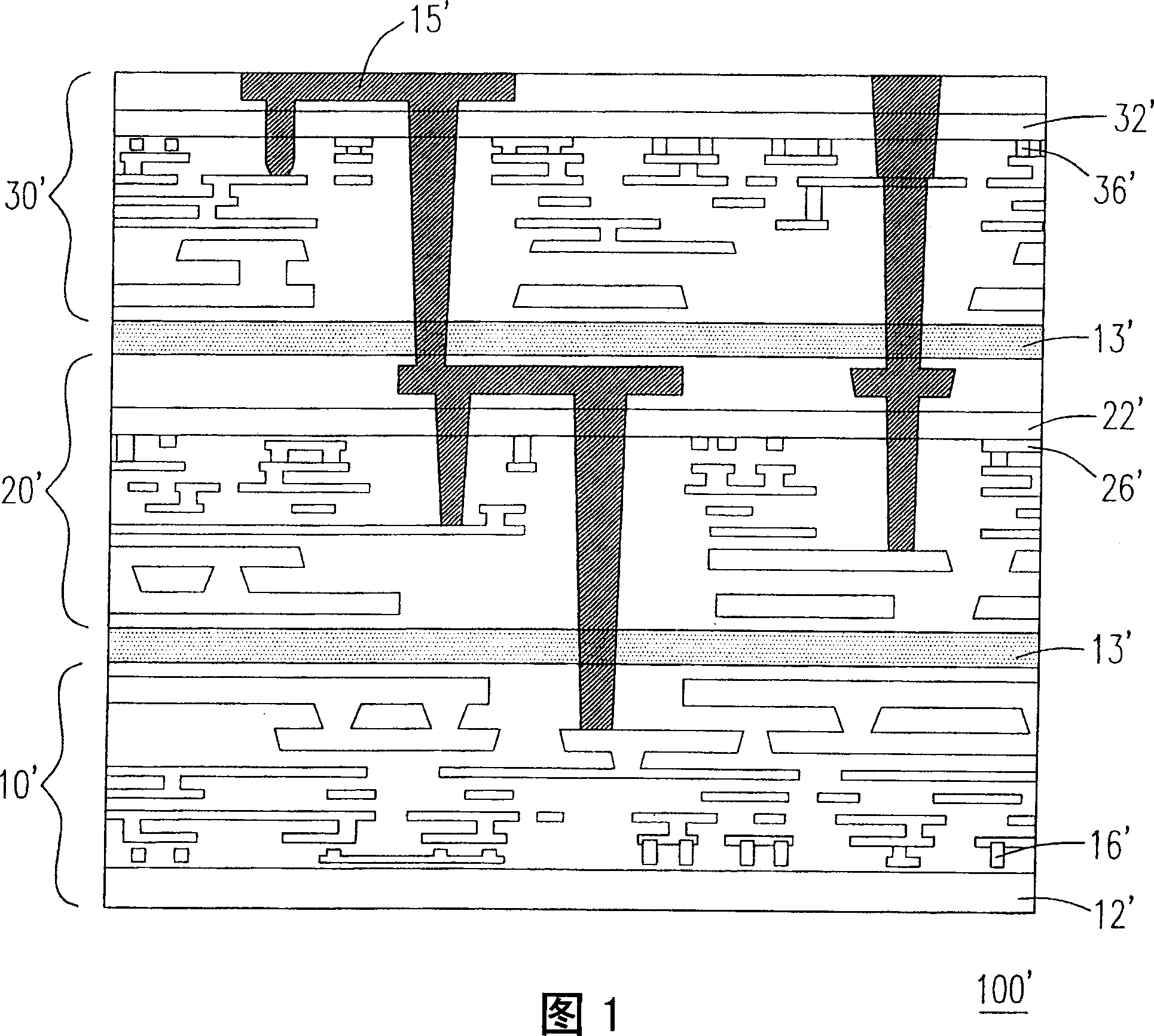

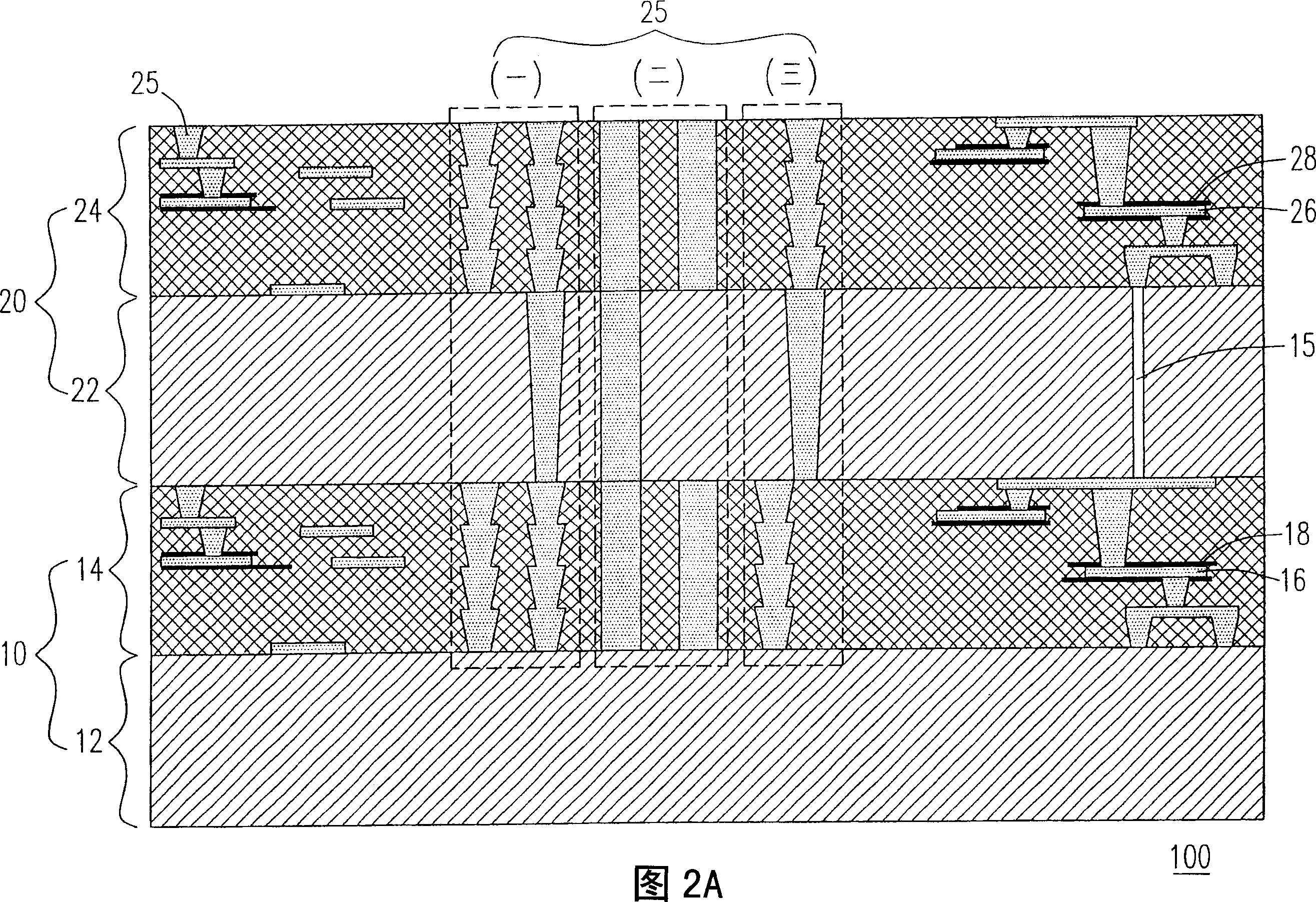

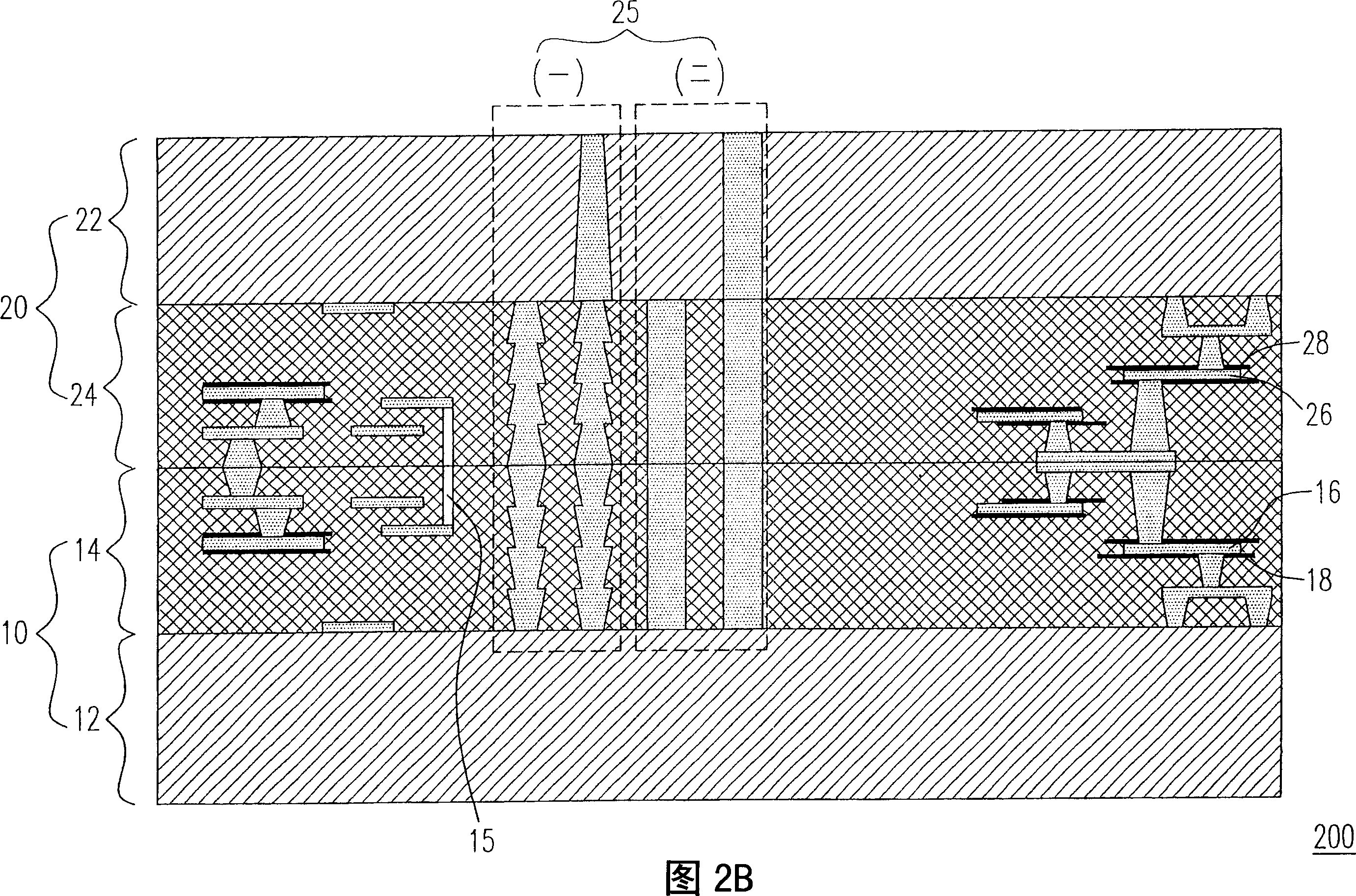

[0063] The three-dimensional wafer stack structure of the present invention uses layer-by-layer deposition or laser drilling to form a metal support structure between two hard surfaces (or substrates) on the wafer to provide support for the structure layer and achieve the purpose of strengthening the low dielectric The purpose of the material layer.

[0064] Please refer to FIGS. 2A-2D , which illustrate various specific embodiments of the three-dimensional wafer stack structure of the present invention. As shown in FIG. 2A, the three-dimensional wafer stack structure 100 of the first embodiment of the present invention is composed of a first wafer 10 and a second wafer 20, wherein the first and second wafers 10, 20 are all facing upwards. (face up) arrangement (or called back to face (back to face or back to front) stacked structure), wherein, the first and second wafers 10, 20 respectively include a first and second substrate layer 12, 22 and a first and a second device lay...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com