Formation of pulse signal from clock signal

A pulse signal and clock signal technology, applied in pulse processing, pulse technology, delay line pulse generation, etc., can solve problems such as reducing the clock signal cycle

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach

[0039] A. The first embodiment;

no. 2 Embodiment ;

[0041] C. The third embodiment;

[0042] D. The fourth embodiment;

[0043] E. The fifth embodiment;

[0044] F. The sixth embodiment;

[0045] G.Modification

no. 1 Embodiment

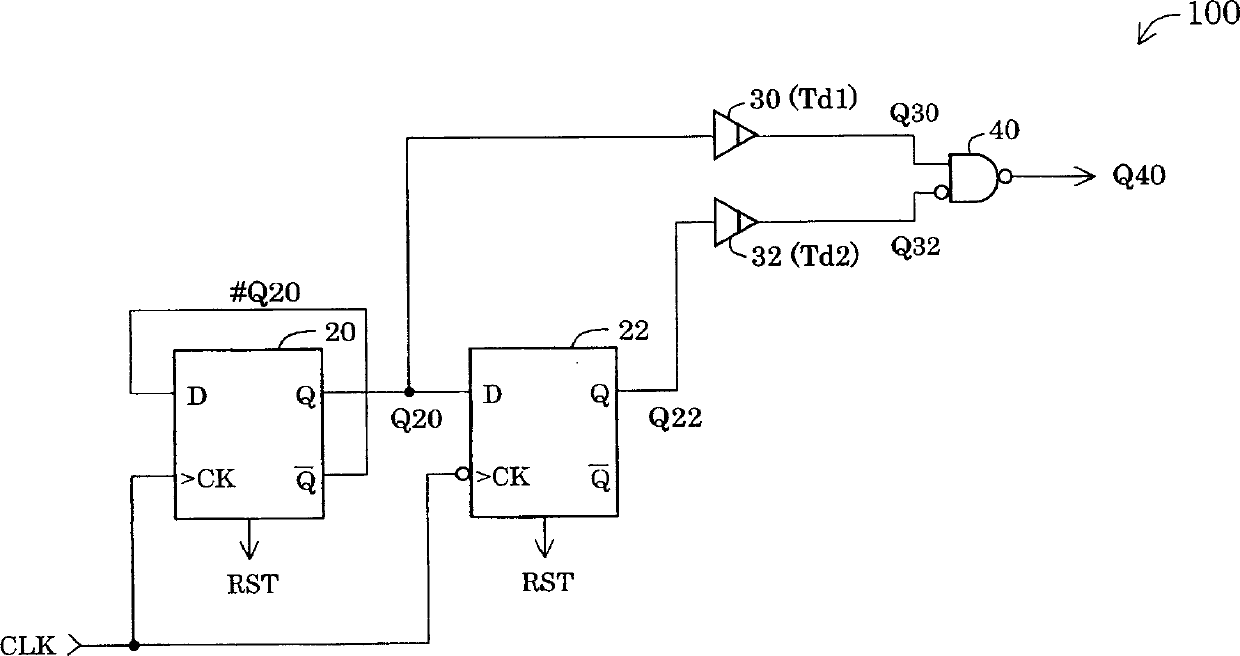

[0047] figure 1 It is a block diagram showing the configuration of the pulse signal generating circuit 100 as the first embodiment of the present invention. This pulse signal generating circuit 100 includes two D flip-flops 20, 22, two delay elements 30, 32, and a NAND gate 40 in which one of the two input terminals is a non-inverting input terminal. In addition, hereinafter, the "D flip-flop" is referred to as "DFF".

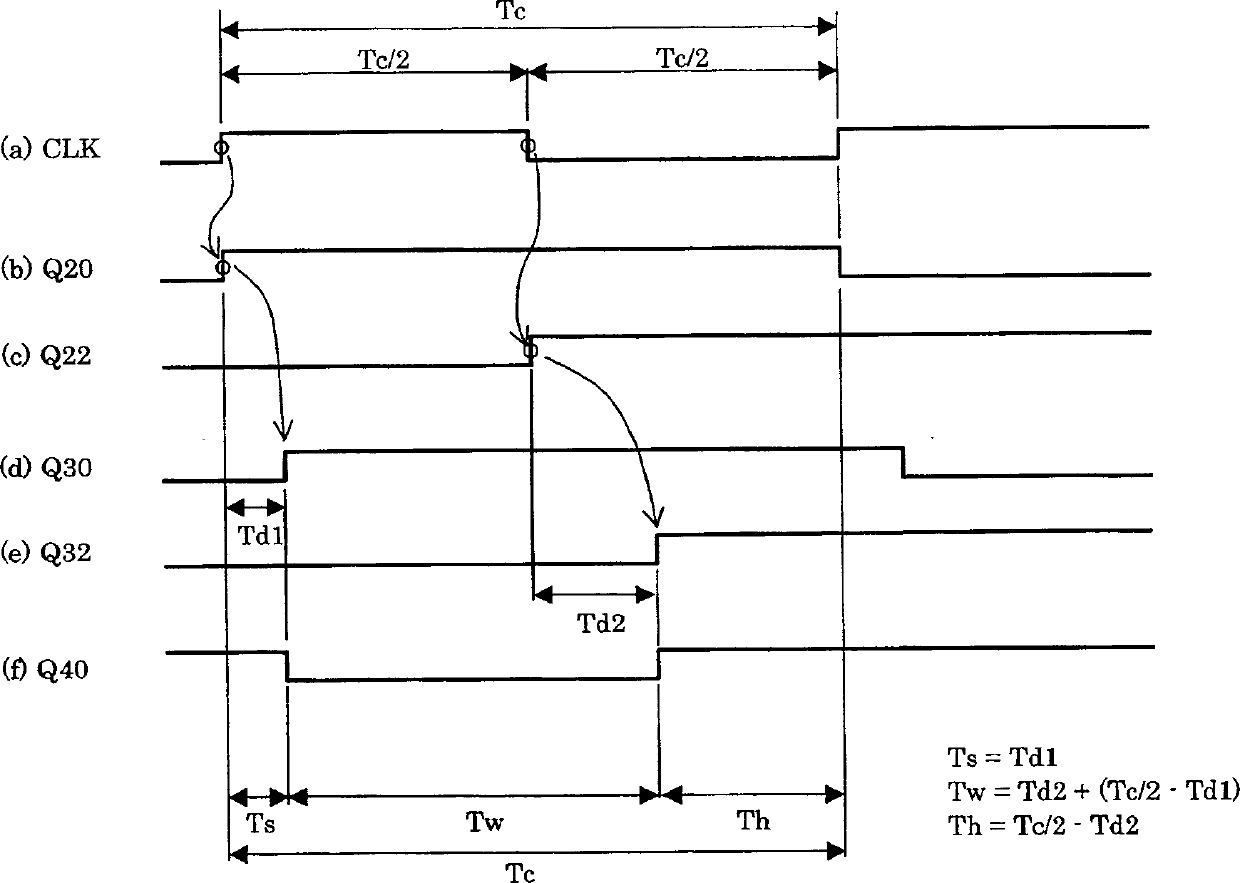

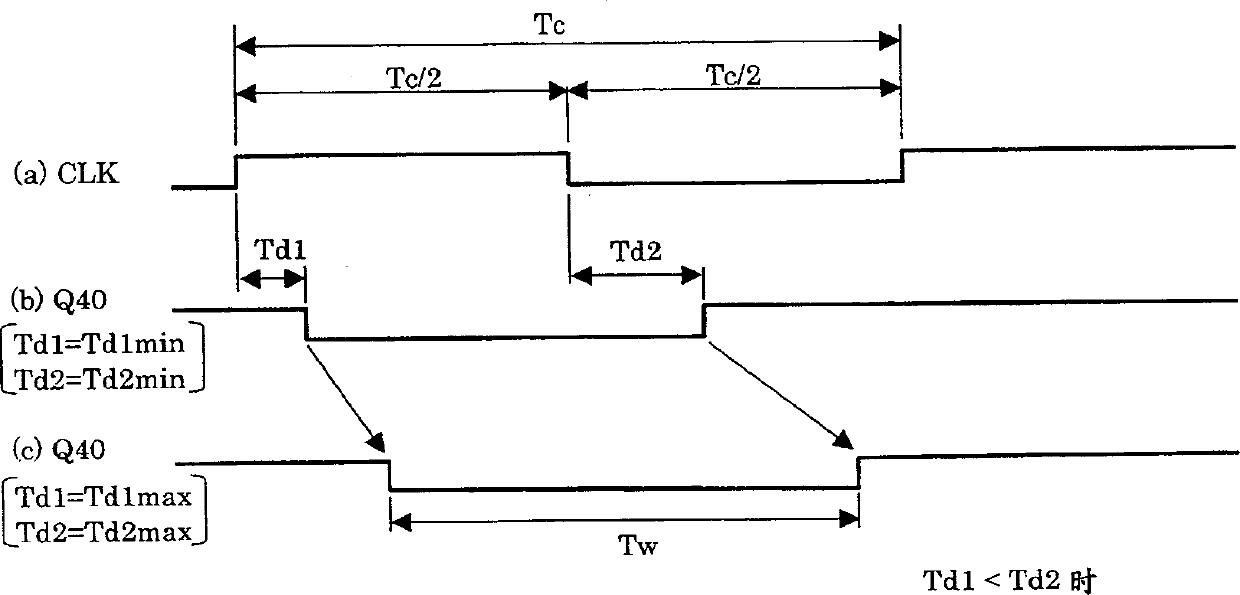

[0048] The clock signal CLK is input to the clock input terminal of the first DFF 20 and input to the clock terminal of the second DFF 22 after being inverted. The inverted output #Q20 of the first DFF20 is fed back to the D input terminal of the first DFF20. The output Q20 of the first DFF 20 is input to the D input terminal of the second DFF 22 and also input to the first delay element 30 . The output Q22 of the second DFF 20 is input to the second delay element 32 . The first delay signal Q30 delayed by the first delay element 30 is input to the non-inv...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com