Hierarchical built-in self-test for system-on-chip design

A technology with built-in self-test and chip, applied in electronic circuit testing, detecting faulty computer hardware, measuring electricity, etc., can solve problems such as no BIST design

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0064] best practice

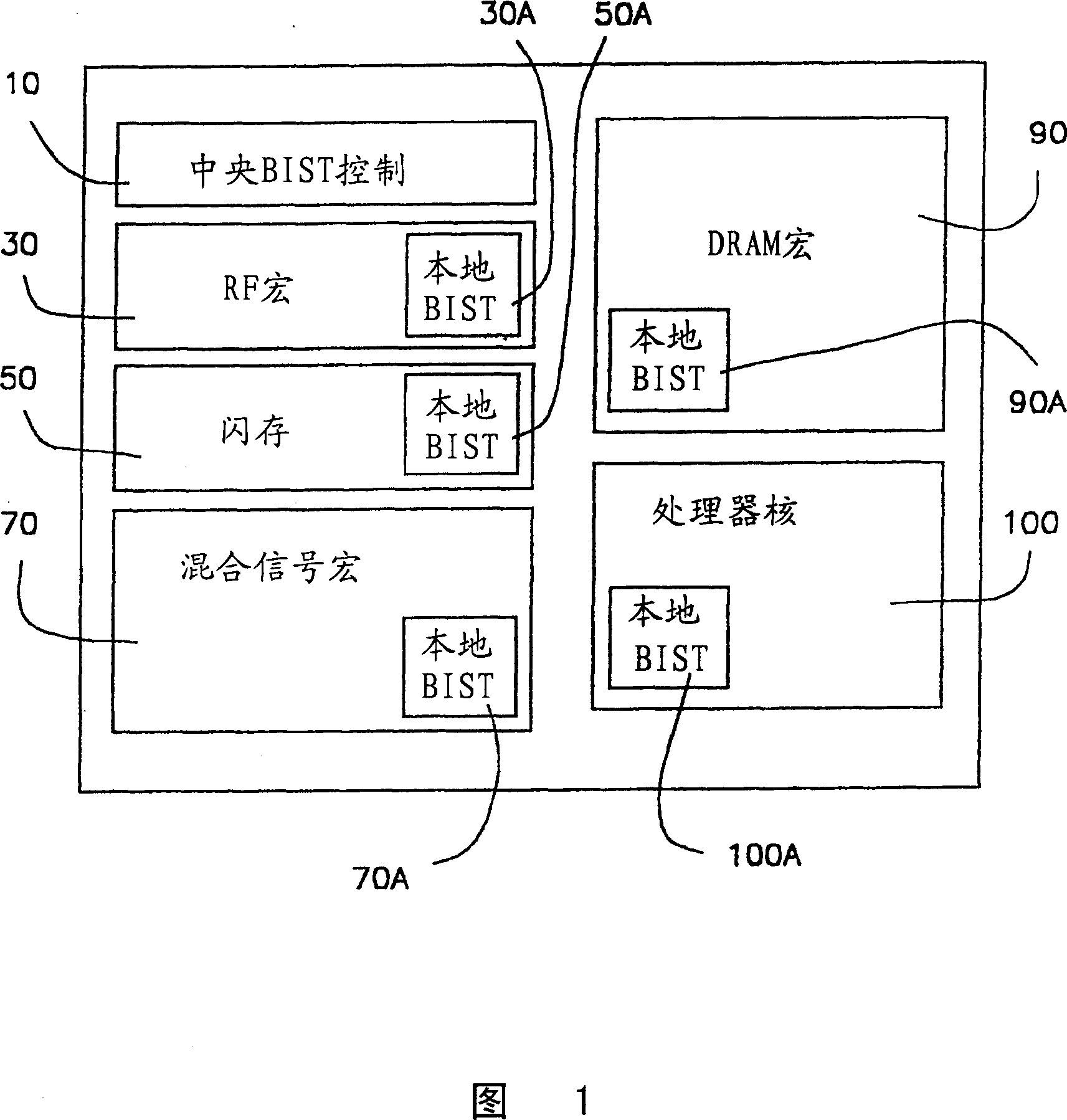

[0065] Figure 1 shows a system-on-chip (SOC) design with specific built-in self-test (BIST) cells. Specifically, the central BIST control unit 10 sends information including address bits and command bits to the local BIST units 30a, 50a, 70a, 90a, 100a of the respective macros 30, 50, 70, 90, 100, respectively, preferably with The following tests are conducted in a graded manner:

[0066] - unit testing of radio frequency (RF) macro 30, flash memory macro 50, mixed signal macro 70, dynamic random access memory macro 90, and processor macro 100;

[0067] - interface testing between the processor macro 100 and the DRAM macro 90, such as reading data from the DRAM to the processor, writing data from the processor to the DRAM, and executing processor test programs from the DRAM macro;

[0068] - Interface test between RF macro 30 and external antenna;

[0069] - Interface testing between the RF macro 30 and the base-band part of the mixed-signal macro 70;...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com