Packaging structure and preparation method thereof

A technology of packaging structure and plastic sealing layer, which is applied in semiconductor/solid-state device manufacturing, semiconductor/solid-state device parts, semiconductor devices, etc., can solve the problems of high cost, chip damage, low yield, etc. The effect of clean mold and simple process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

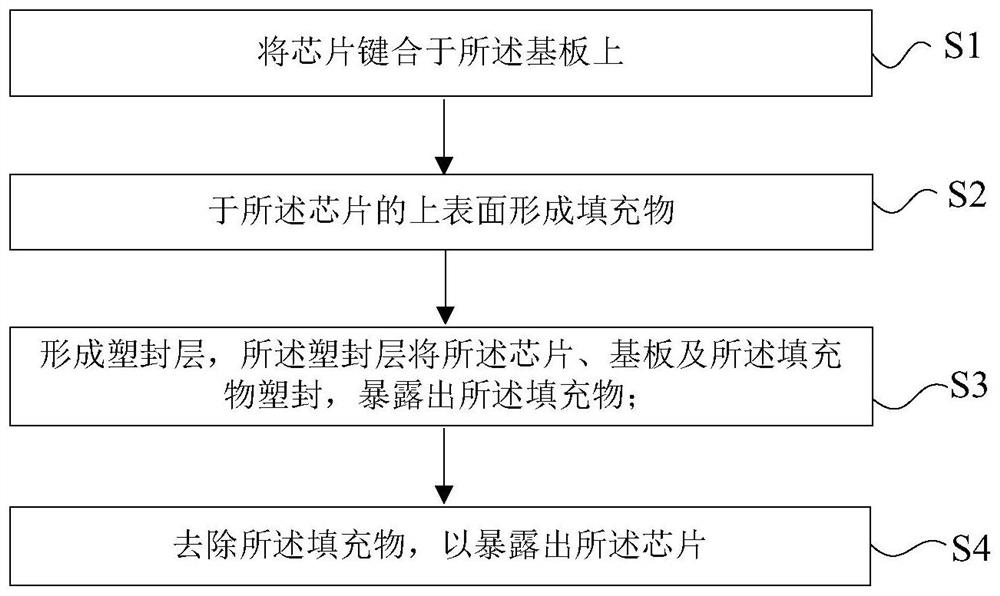

[0026] see figure 1 As shown, the present invention provides a method for preparing an encapsulation structure, comprising the steps of:

[0027] S1: bonding the chip on the substrate;

[0028] S2: forming a filler on the upper surface of the chip;

[0029] S3: forming a plastic sealing layer, the plastic sealing layer plastic sealing the chip, the substrate and the filler, exposing the filler;

[0030] S4: removing the filler to expose the chip.

[0031] The present invention is aimed at the surface exposed die (chip) packaging process, chooses to use the filler, and then takes it out after plastic sealing, avoiding the use of special-shaped molds, the size of the filler can be adjusted arbitrarily, the cost is low, and the process is simple; at the same time, the filler of the present invention The demoulding is clean, and there will be no filler residue on the surface of the chip.

Embodiment 2

[0033] Please combine figure 1 refer to Figures 2 to 7 , this embodiment also provides a method for preparing a packaging structure. The specific structure in this embodiment is roughly the same as that of the method for preparing the packaging structure in Embodiment 1. The difference between the two is that the packaging in this embodiment Compared with the method for preparing the packaging structure in Embodiment 1, the method for preparing the structure includes more and more detailed process steps.

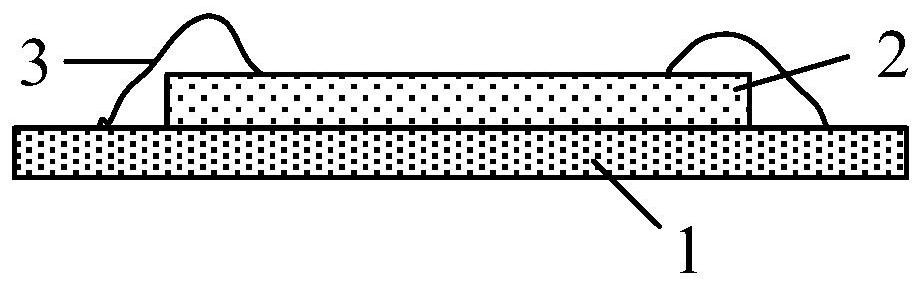

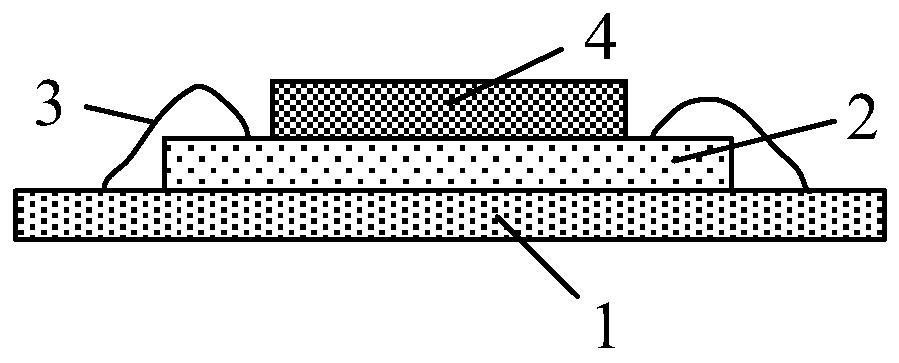

[0034] In step S1, the substrate 1 may include but not limited to PCB (Printed Circuit Board, printed circuit board).

[0035] Specifically, the chip 2 may be any chip with a device structure formed therein. More specifically, the device structure may be formed on the front side of the chip 2 .

[0036] In step S1 , the chip 2 may be mounted on the substrate 1 upright, that is, the chip 2 is bonded on the substrate 1 with its front facing up.

[0037] Such as figure 2...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com