A high-energy-efficiency high-speed parallel ldpc encoding method and encoder

An encoding method and energy-efficient technology, applied in the field of energy-efficient high-speed parallel LDPC encoding methods and encoders, can solve problems such as low throughput, large frame delay, and high resource consumption, so as to reduce hardware resource consumption and simplify implementation methods , the effect of reducing the number of operands

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

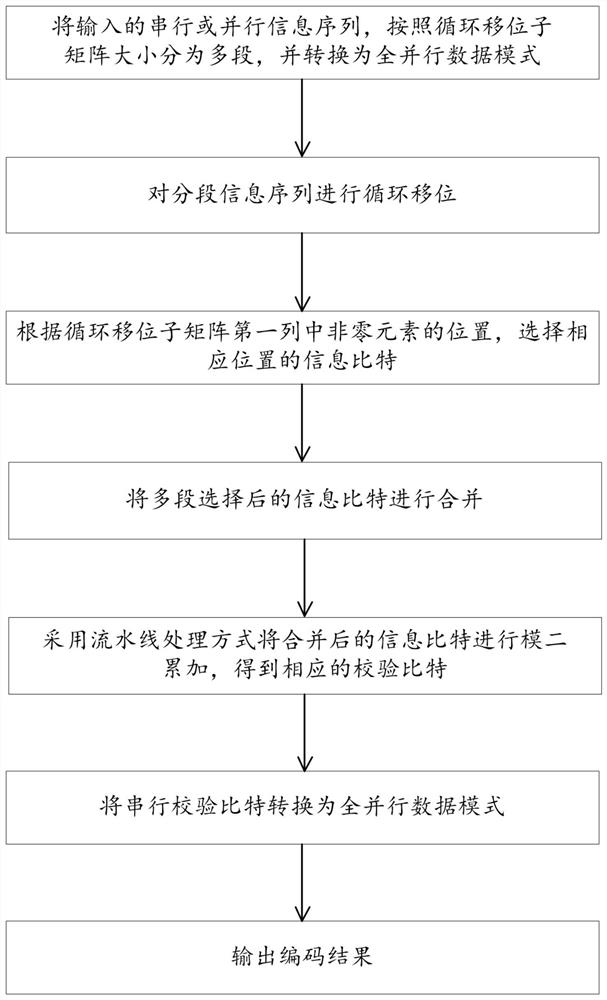

[0056] Embodiments of the present invention provide a high-speed parallel LDPC coding method with high energy efficiency, such as figure 1 As shown, the method includes the following steps:

[0057] Divide the input serial or parallel information sequence into multiple segments according to the size of the quasi-cyclic LDPC code cyclic shift sub-matrix, and convert it into a full parallel data mode;

[0058] Perform cyclic shift on the segmented information sequence;

[0059] According to the position of the non-zero element in the first column of the cyclic shift sub-matrix, select the information bit of the corresponding position;

[0060] Combining the selected information bits of multiple segments;

[0061] The merged information bits are subjected to modulo two accumulation by means of pipeline processing to obtain the corresponding parity bits;

[0062] Convert serial parity bits to full parallel data mode;

[0063] Output the encoding result.

[0064] According to ...

Embodiment 2

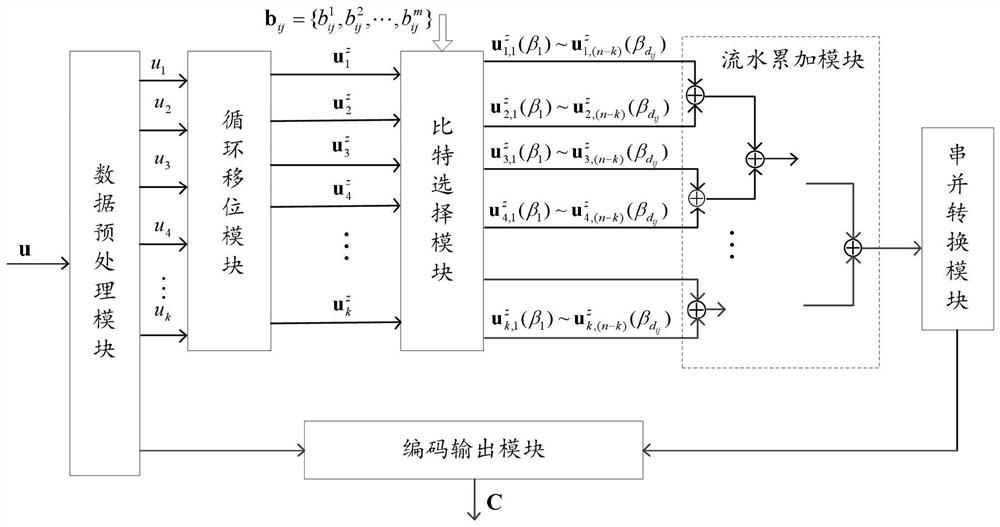

[0088] Correspondingly, the present invention also provides an LDPC encoder based on the above-mentioned high-speed parallel LDPC encoding method with high energy efficiency, such as figure 2 As shown, the encoder includes:

[0089] The data preprocessing module is used to divide the input serial or parallel information sequence into multiple segments according to the size of the cyclic shift sub-matrix in the generation matrix, and convert it into a full parallel data mode;

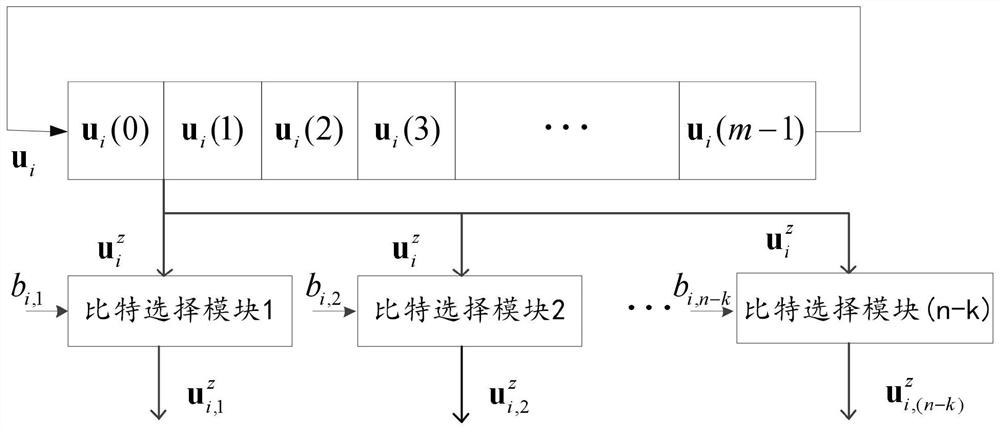

[0090] Multiple cyclic shift modules are used to cyclically shift the segmented information sequence;

[0091] A plurality of bit selection modules are used to select the information bits at the corresponding positions according to the positions of the non-zero elements in the first column of the cyclic shift sub-matrix;

[0092] Multiple bit merging modules are used to combine the outputs of multiple bit selection modules;

[0093] The pipeline accumulation module is used for adopting the pipeline pr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com