Verification method of APB-UART module based on UVM

An APB-UART and verification method technology, applied in the field of verification of protocol conversion modules, can solve the problems of incompetence for verification of complex function modules, low verification efficiency, low reusability, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

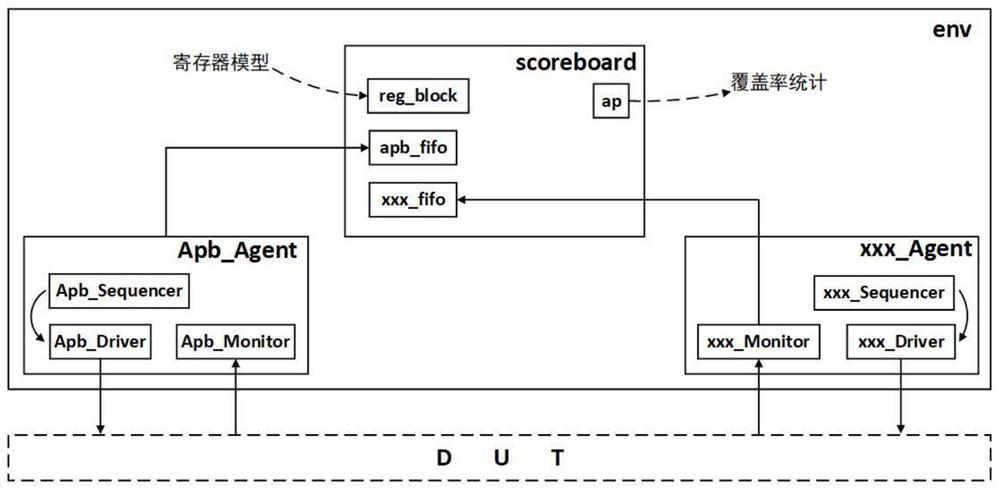

[0019] The overall structure of this verification platform is as follows: figure 1 As shown, the specific implementation of each module is as follows.

[0020] This verification platform uses agents to drive and collect specific ports. It contains four agents in total, namely Apb_Agent, Rx_Agent, Tx_Agent and Modem_Agent. Both Rx_Agent and Tx_Agent are instantiated by Uart_Agent. As can be seen in the overall architecture diagram, different agents encapsulate the corresponding driver, monitor, and sequencer. Each agent realizes the conversion of data from transaction level to signal level through the corresponding driver component, and drives it to the relevant port of DUT; through the corresponding monitor component, it collects the relevant port signal at a specific moment, and converts it from signal level to transaction level and sends it It is used for subsequent modules; through the corresponding sequencer, the work of generating different incentives is separated, and t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com