Downlink bit-level processing method based on fpga hardware acceleration

A downlink and hardware acceleration technology, applied in electrical components, program control, instruments, etc., can solve the problems of data disorder and loss design difficulty, increase of mobile communication system delay, and reduce algorithm design difficulty, etc., to achieve real-time high-speed The effect of processing, real-time improvement and delay reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0011] The present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments.

[0012] The existing general-purpose processor platform implements the operation processing of the entire link on the CPU, which takes a lot of time when faced with complex calculations. The invention realizes the downlink bit-level data processing by FPGA, thereby reducing the signal processing time delay, and improving the processing capability of the large-capacity data of the virtualized gateway station and the real-time performance of communication transmission.

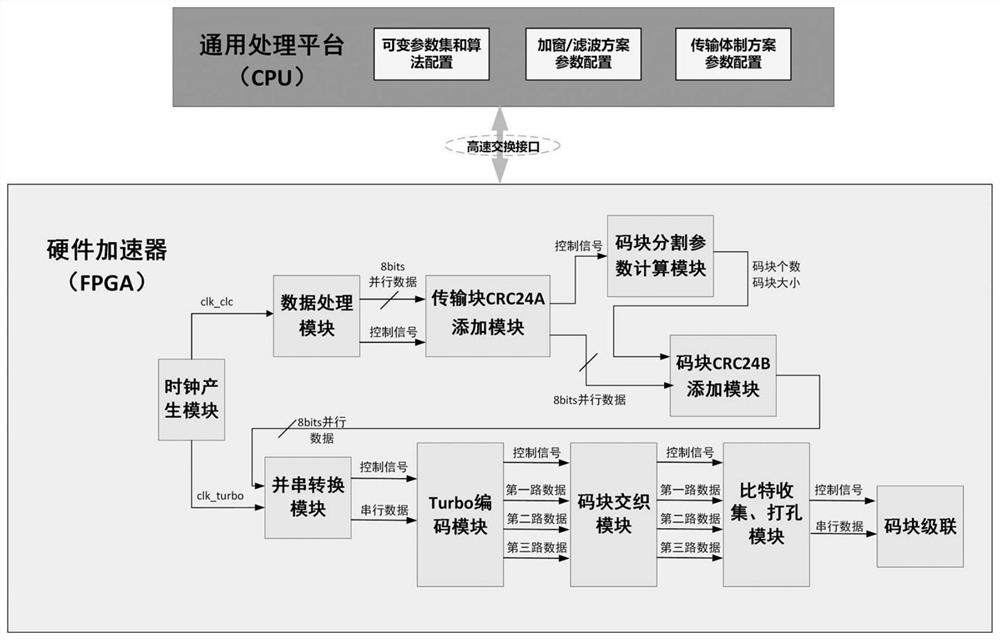

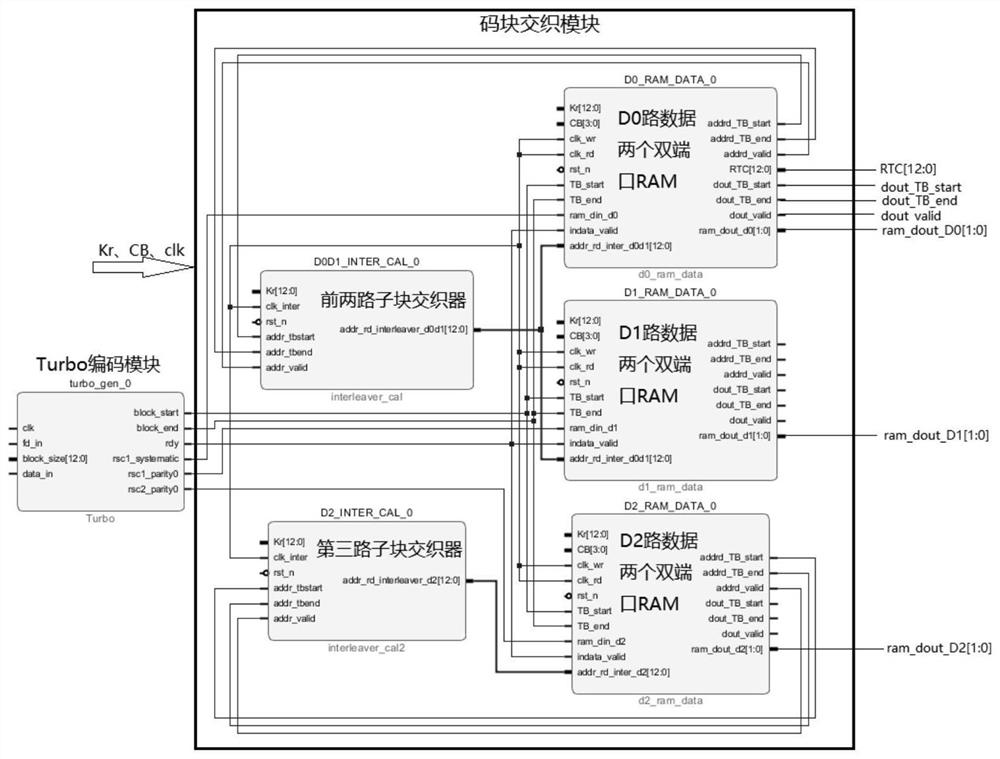

[0013] like figure 1 As shown, the downlink PDSCH bit-level processing method based on FPGA hardware acceleration of the present invention is realized based on the combination of a general-purpose processing platform CPU and a hardware accelerator FPGA; wherein, the general-purpose processing platform CPU mainly completes the selection of the communication transmission system, th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com