Controllable tracking debugging method and system for RISC-V processor

A RISC-V, trace debugging technology, applied in electrical digital data processing, software testing/debugging, instruments, etc., can solve the problems of inflexible acquisition of RISC-V processors, reduce debugging cycle, reduce debugging difficulty, etc. The effect of reducing the need for long-term tracking and debugging, reducing the debugging cycle, and reducing the difficulty of debugging

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

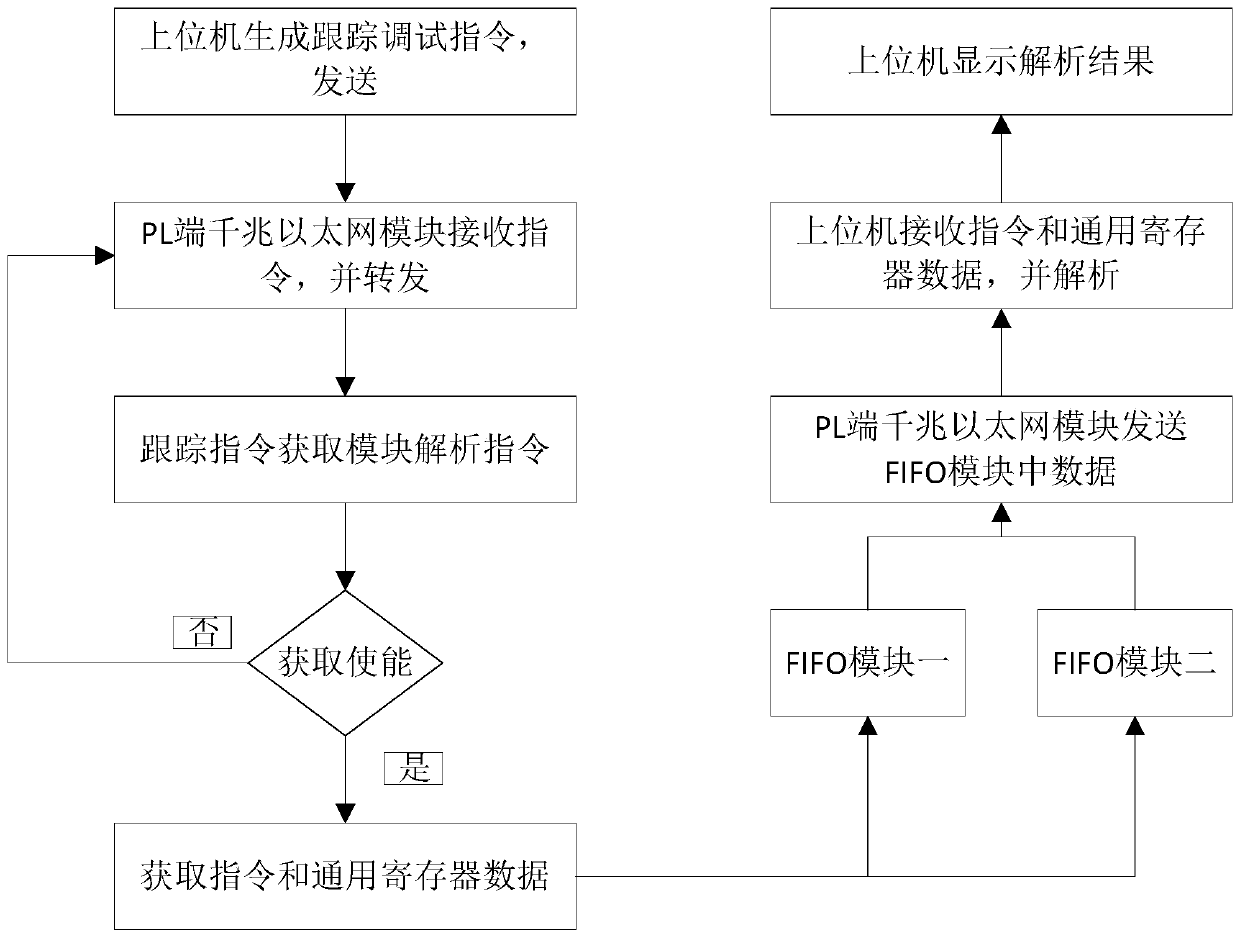

[0043] as attached figure 1 As shown, the controllable tracking debugging method of the RISC-V processor of the present invention, the method steps are as follows:

[0044] S1. The upper computer generates the enable signal for tracking and debugging instructions and general register data acquisition and the address of the general register to be obtained, packs and debugs the tracking instructions, and sends them to the PL terminal through the Gigabit Ethernet interface; wherein, the debugging and tracking instructions include acquiring instructions. Enable and disable signals and register codes for obtaining general-purpose register data. By enabling and disabling signals for debugging and tracking instructions, the time point for obtaining instructions can be effectively controlled, reducing the amount of instruction analysis data in the later stage; the production and sending time of debugging and tracking instructions can be shortened. Control, which can be set by the debu...

Embodiment 2

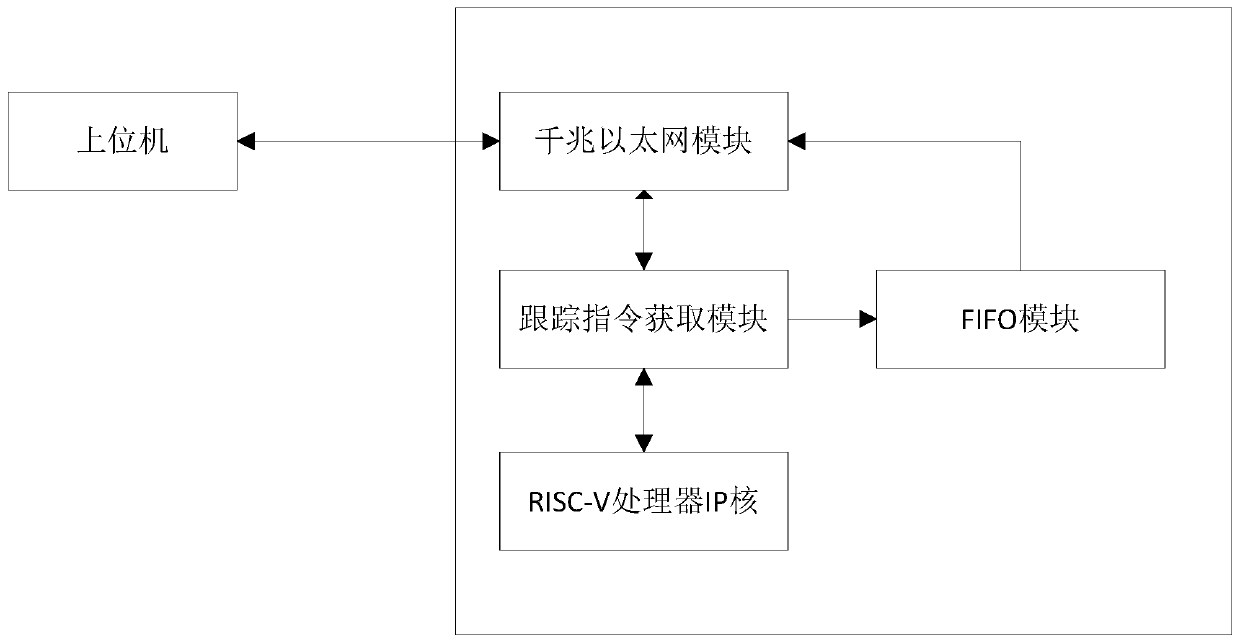

[0058] as attached figure 2 Shown, the controllable tracking debugging system of RISC-V processor of the present invention, this system comprises upper computer, Gigabit Ethernet module, tracking instruction acquisition module, FIFO module and RISC-V processor IP core, upper computer and gigabit The Gigabit Ethernet module communicates with each other, the Gigabit Ethernet module communicates with the tracking instruction acquisition module, the tracking instruction acquisition module communicates with the RISC-V processor IP core, and the tracking instruction acquisition module stores data to the FIFO module, and the FIFO module sends data to Gigabit Ethernet module;

[0059] Among them, the upper computer is used to generate the enable signal for tracking and debugging instructions and general register data acquisition, as well as the address of the general register to be obtained, package the debugging and tracking instructions, and send them to the PL terminal through the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com