Butt coupling method used for monolithic integrated chip

A single-chip integration and docking coupling technology, which is applied in the field of docking coupling, can solve the problems of low coupling efficiency affecting the optical power of the device, affecting the transmission characteristics of the device, and poor refractive index, so as to improve the quality of docking coupling, improve growth quality, and reduce loss. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] The solutions of the present invention will be further described below in conjunction with the accompanying drawings and embodiments.

[0041] This embodiment discloses a butt coupling method for monolithic integrated chips, including the following steps:

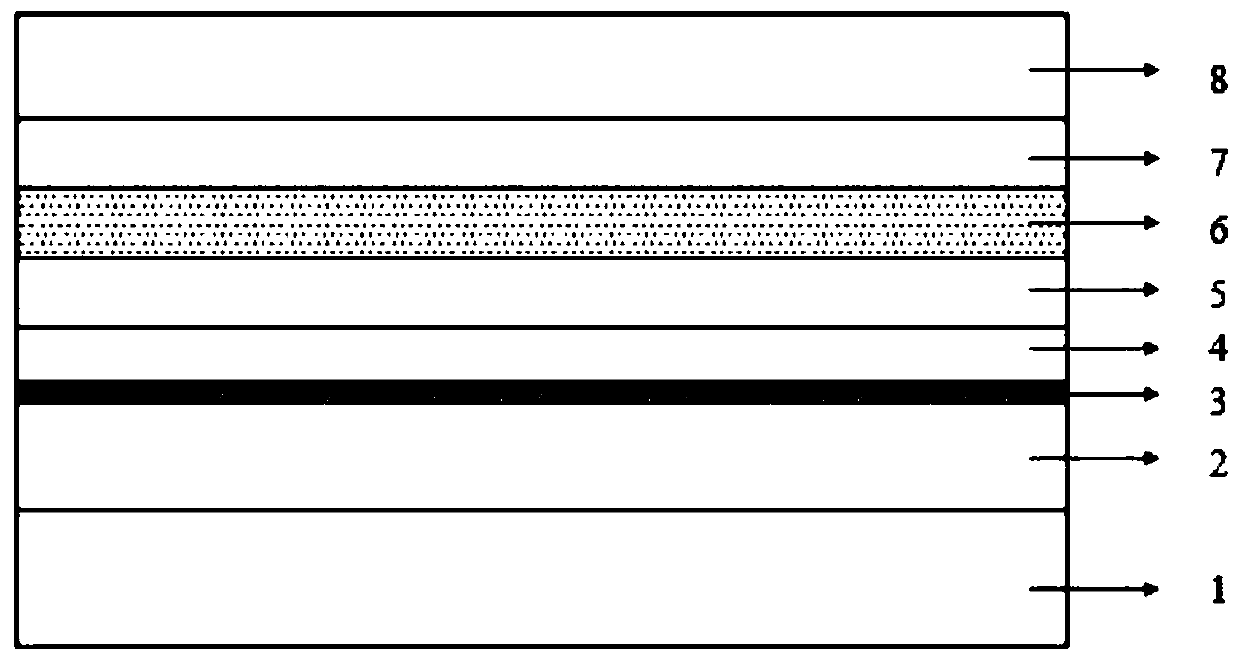

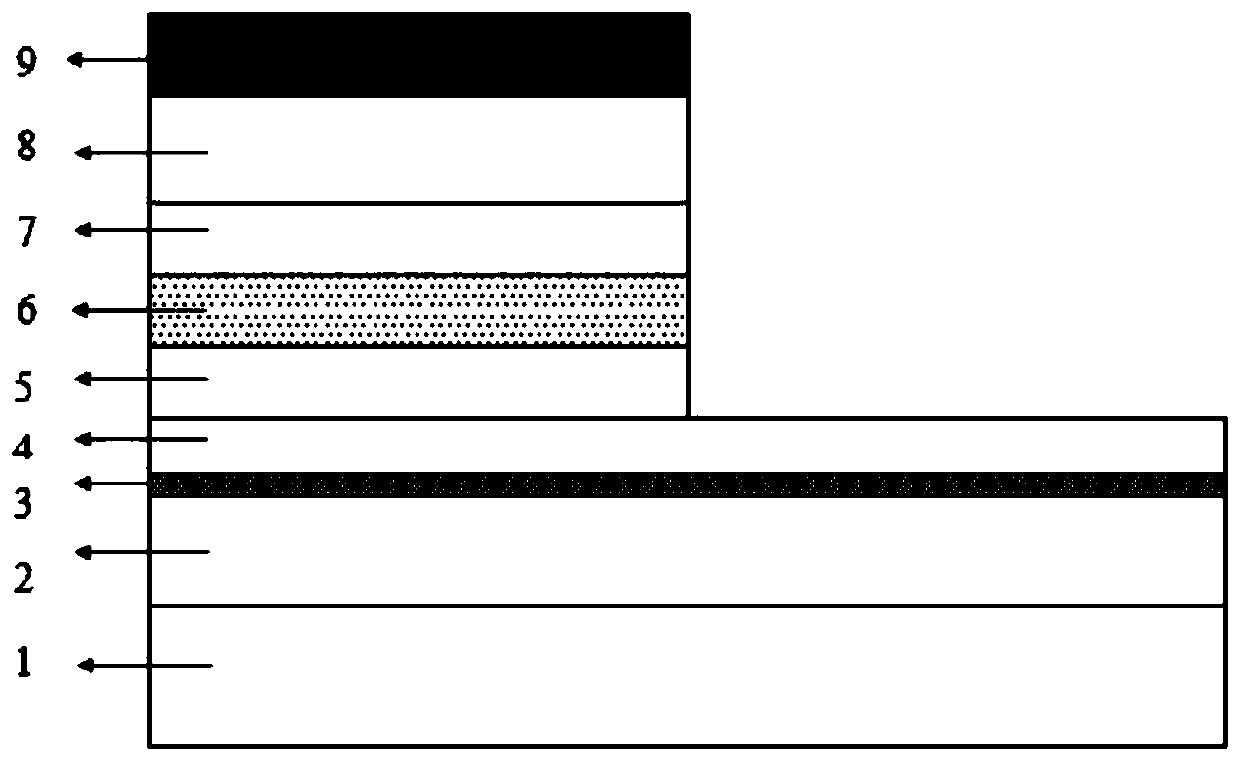

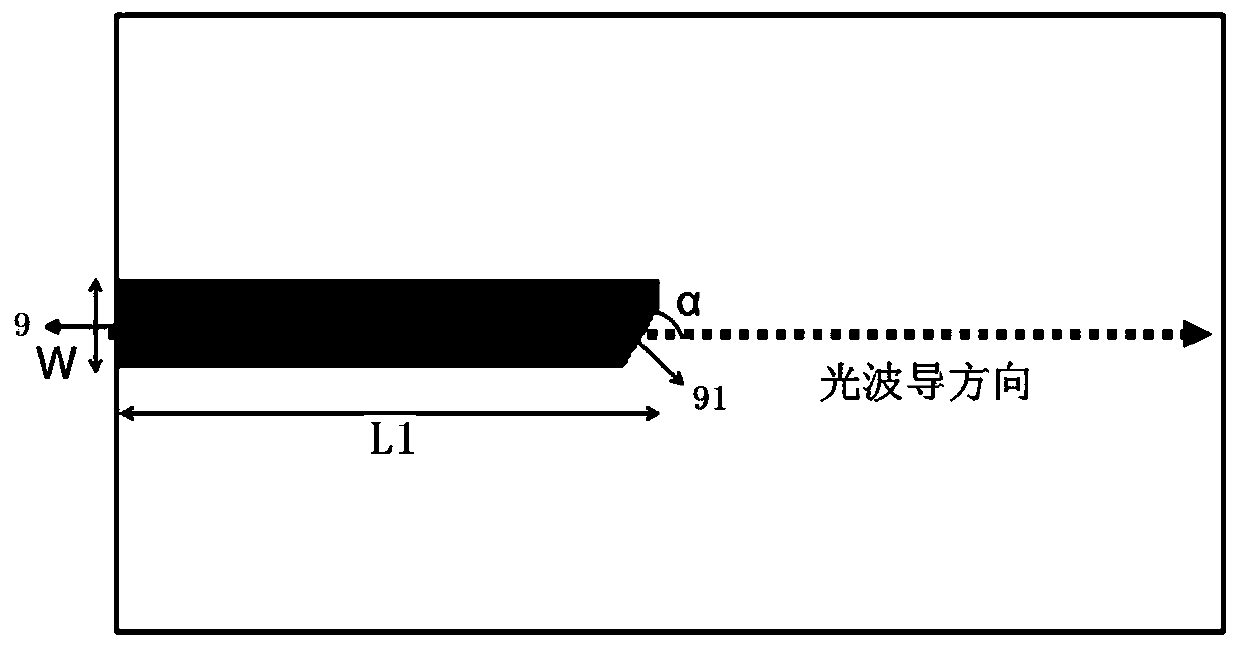

[0042] S1) if figure 1 , growing the first functional device on the substrate 1, including sequentially growing the first InP buffer layer 2, the quaternary optical field control layer 3, the second InP buffer layer 4, the first lower waveguide layer 5, and the first active quantum well Layer 6, first upper waveguide layer 7, first InP cladding layer 8;

[0043] Among them, the material composition of the quaternary optical field control layer 3 is 120-180nm different from the PL of the active MQW, and its function is to control the optical field of the first functional device in the active / passive waveguide of the second functional device to avoid The light leakage of the substrate can be used as an etching stop l...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com