A ferroelectric field effect transistor and its preparation method

An electric field effect and transistor technology, applied in the field of ferroelectric field effect transistors and their preparation, can solve problems such as reliability problems and insufficient process, and achieve the effect of promoting ferroelectricity and avoiding lattice distortion.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

[0070] According to another aspect of the present invention, there is provided a method for preparing a ferroelectric field effect transistor, comprising:

[0071] S1: Divide the substrate layer into a source region, a drain region and an insulating region;

[0072] S2: perform ion implantation treatment in the source region and the drain region and activate the ion implantation region;

[0073] S3: sequentially arrange a gate insulating layer, a first buffer layer, an intermediate dielectric layer, a second buffer layer and a gate electrode layer on the insulating region;

[0074] S4: Etch contact holes in both the source region and the drain region, and fill the contact holes with electrodes to obtain semi-finished products with electrodes;

[0075] S5: adopting high temperature annealing to activate the intermediate dielectric layer, the first buffer layer and the second buffer layer to fully generate element diffusion and interfacial reaction on the semi-finished product ...

Embodiment 1

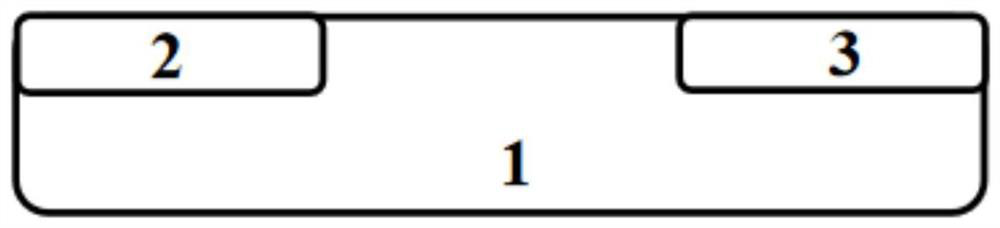

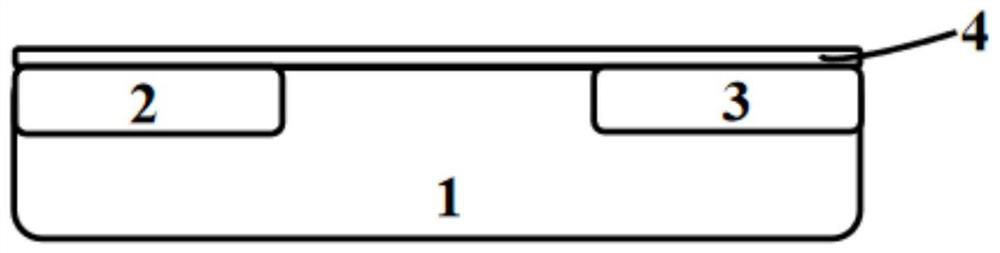

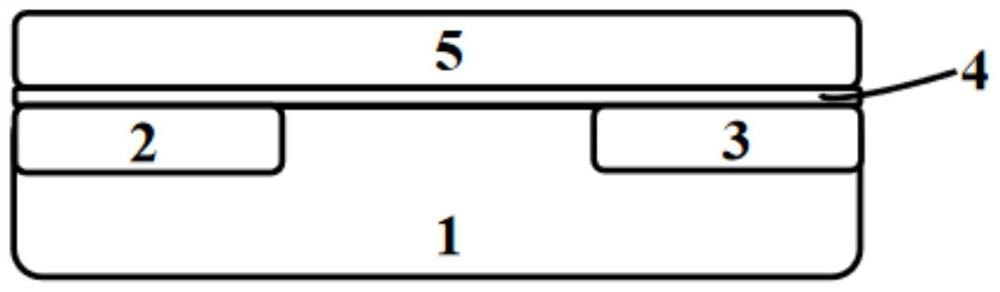

[0090] An optional embodiment of the present invention provides a ferroelectric field effect transistor that makes full use of element diffusion and interface reaction to prepare hafnium oxide-based ferroelectric field effect transistors. In this embodiment, the hafnium oxide-based ferroelectric field effect transistor includes: a horizontally arranged lining The bottom layer 1, the source region 2 and the drain region 3 located on the substrate layer 1 and separately arranged, the gate insulating layer 4 located between the source region 2 and the drain region 3, the first buffer layer 5, in the first buffer The intermediate dielectric layer 6 , the second buffer layer 7 , the gate electrode layer 8 on the layer 5 , and the source electrode 9 and the drain electrode 10 are formed on the source region 2 and the drain region 3 .

[0091] The horizontally arranged substrate layer 1 consists of p-type doped Si (p-Si) material;

[0092] The gate insulating layer 4 is made of silic...

Embodiment 2

[0108] An optional embodiment of the present invention provides a ferroelectric field effect transistor that makes full use of element diffusion and interface reaction to prepare hafnium oxide-based ferroelectric field effect transistors. In this embodiment, the hafnium oxide-based ferroelectric field effect transistor includes: a horizontally arranged lining The bottom layer 1, the source region 2 and the drain region 3 located on the substrate layer 1 and separately arranged, the gate insulating layer 4 located between the source region 2 and the drain region 3, the first buffer layer 5, in the first buffer The intermediate dielectric layer 6 , the second buffer layer 7 , the gate electrode layer 8 on the layer 5 , and the source electrode 9 and the drain electrode 10 are formed on the source region 2 and the drain region 3 .

[0109] The horizontally arranged substrate layer 1 is composed of p-type doped Si (p-Si) material;

[0110] The gate insulating layer 4 is composed o...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com