Flow control type FIFO cache structure and method for uniformly configuring data significant bits

A technology for effective data and configuration registers, applied in electrical digital data processing, instruments, etc., to achieve the effect of reducing auxiliary operation overhead and avoiding overflow errors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

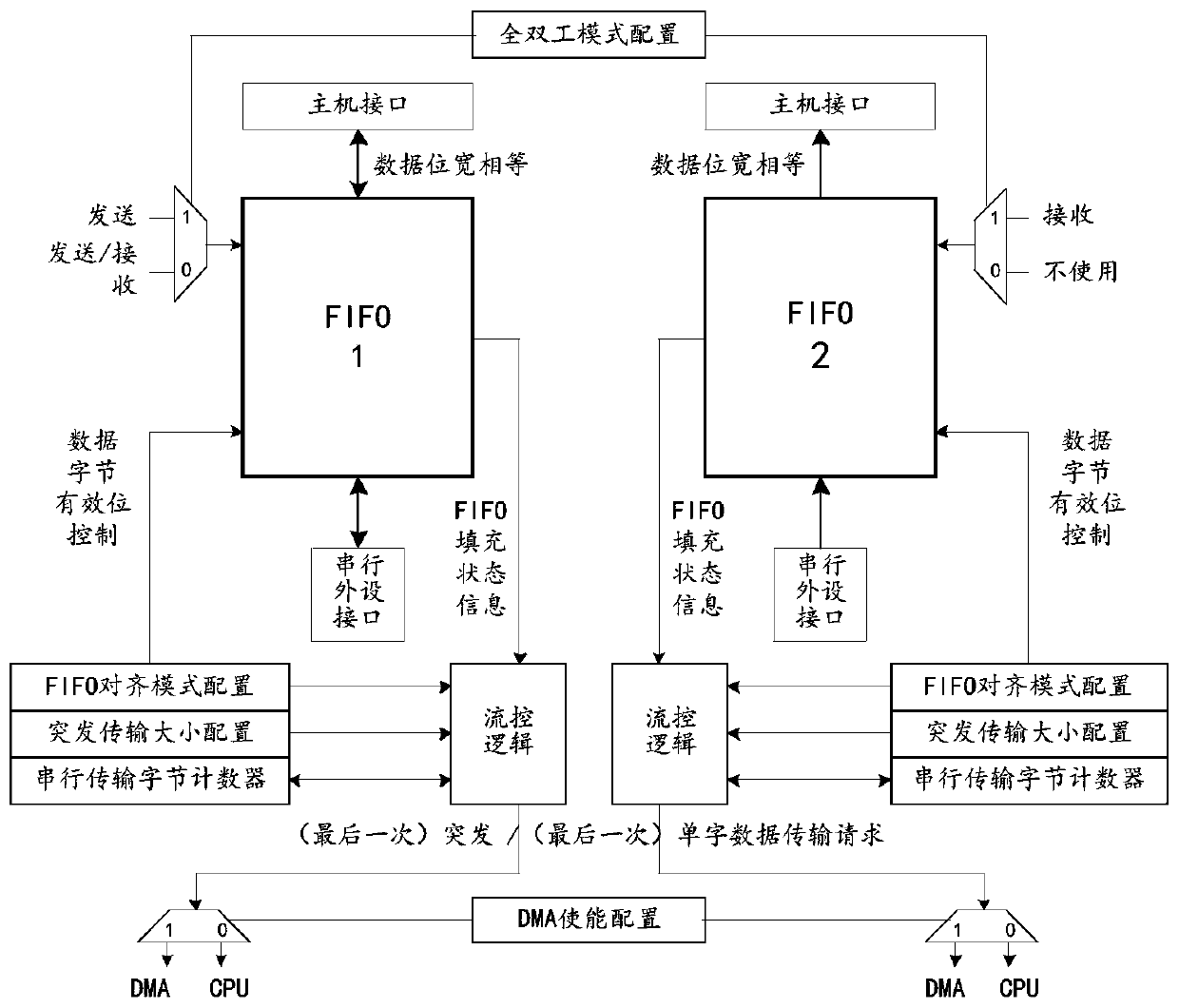

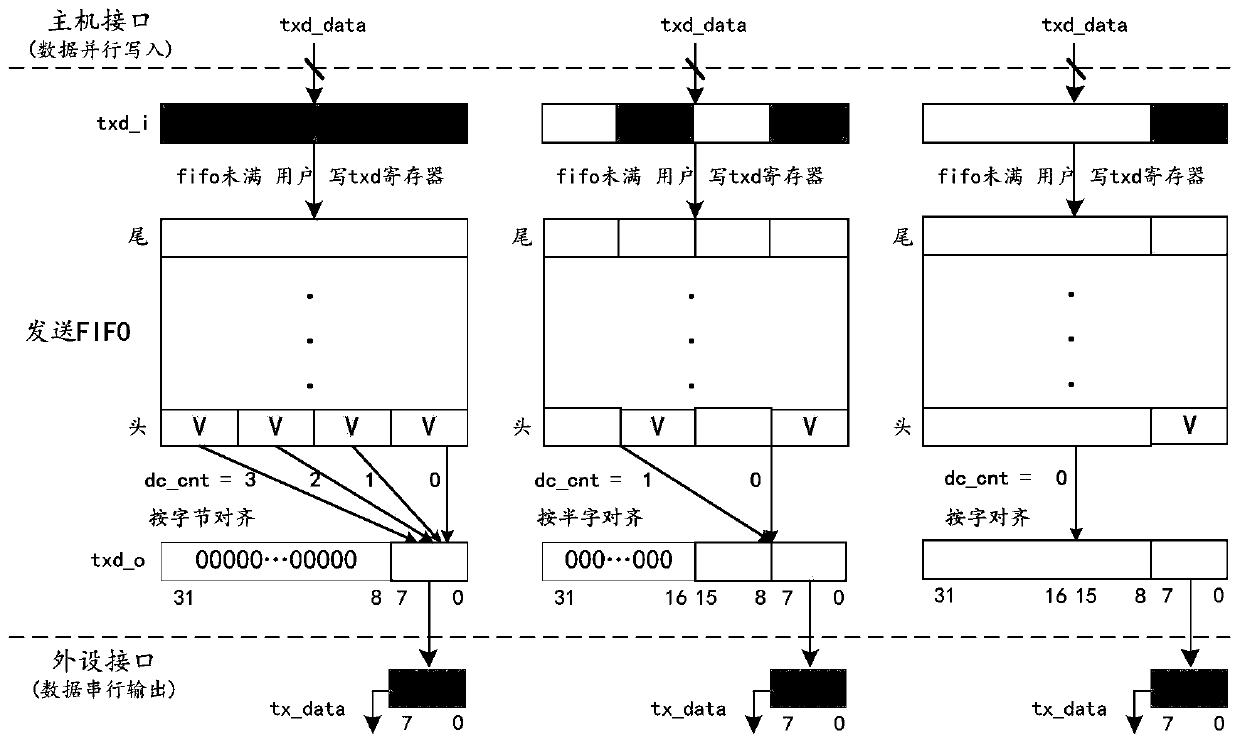

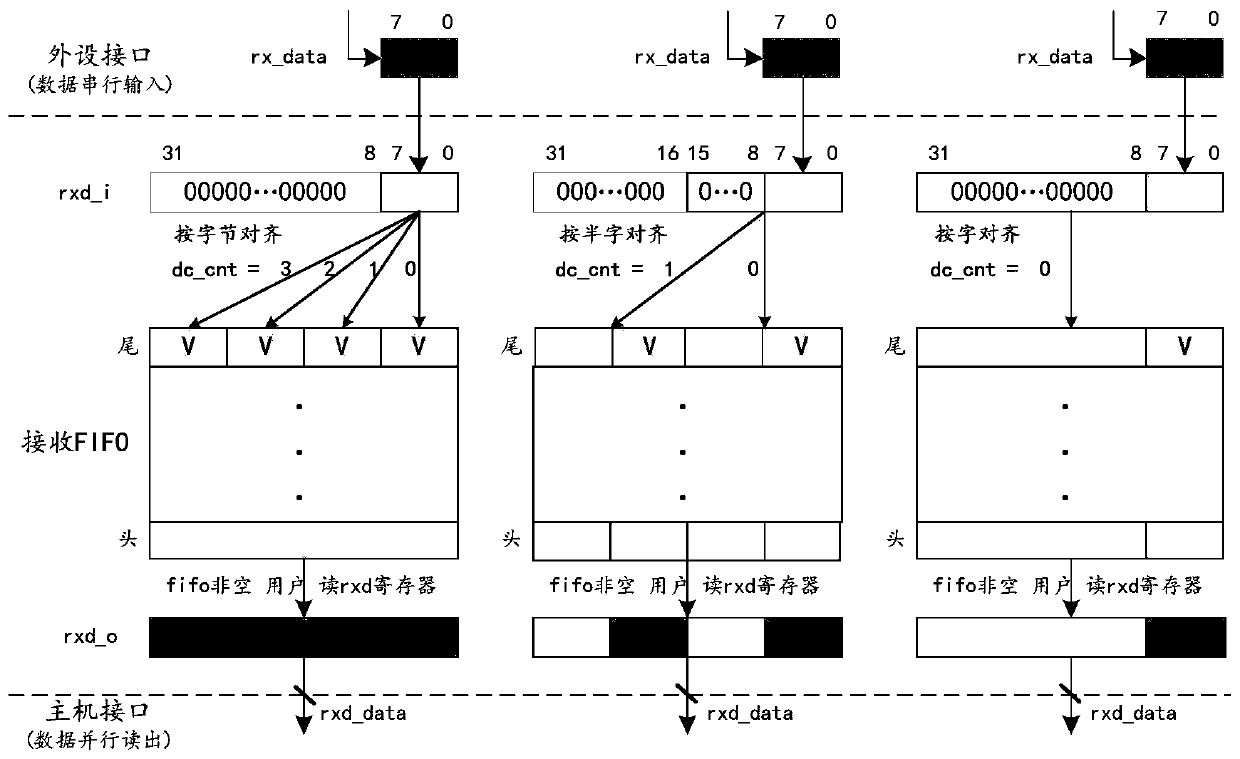

Method used

Image

Examples

Embodiment

[0056] The present invention is applied to the design of I2C serial bus controllers of multiple SoC chips. These SoCs adopt the host control interface of 32-bit SPARC V8 processor, so the FIFO storage bit width in the I2C bus controller is also 32 bits. By using the content of the invention, the data transmission efficiency between the I2C module and the host SPARC V8 processor is obviously improved, and no I2C FIFO overflow error occurs, thereby improving application reliability.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com