FPGA implementation method and system of a FARROW type filter

An implementation method and filter coefficient technology, applied in the field of FPGA implementation system, can solve the problems of high price ratio of bit width and high price ratio of ROM resources, and achieve the effect of small error, reduced possibility of overflow, and resource saving.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] The preferred embodiments of the present invention will be further described in detail below in conjunction with the accompanying drawings.

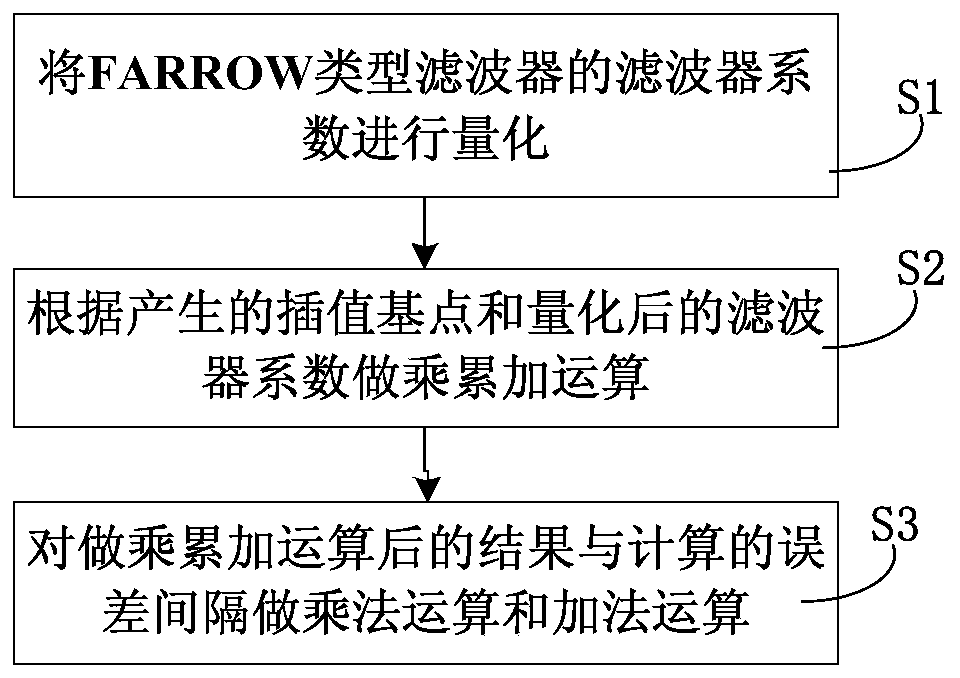

[0036] Such as figure 1 As shown, this example provides an FPGA implementation method of a FARROW type filter, including the following steps:

[0037] Step S1, set the filter coefficient coeff of the FARROW type filter according to 2 k Quantify;

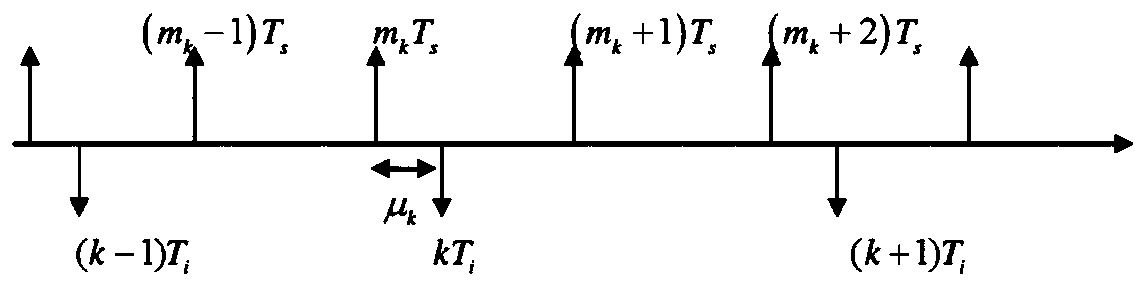

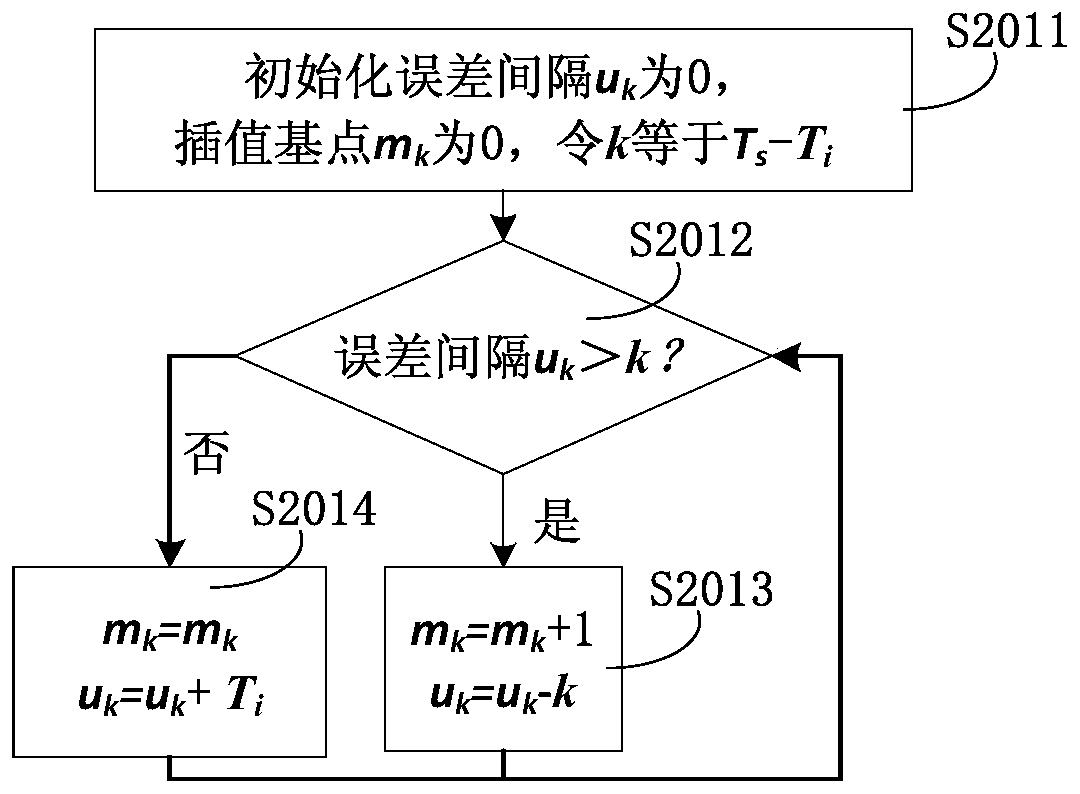

[0038] Step S2, according to the calculation error interval u k The interpolation base point m generated when k Perform multiplication and accumulation operations with the quantized filter coefficient coeffL;

[0039] Step S3, the error interval u between the result after the multiplication and accumulation operation and the calculation k Do multiplication and addition.

[0040] In step S1 described in this example, by formula coeffL=floor(coeff·2 k / T s ) Quantize the filter coefficient coeff of the FARROW type filter to obtain the quantized filter coefficient coeffL, where flo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com