Semiconductor device and method for manufacturing semiconductor device

A semiconductor and substrate technology, applied in semiconductor devices, electrical components, circuits, etc., can solve problems such as breakdown and failure to maintain withstand voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

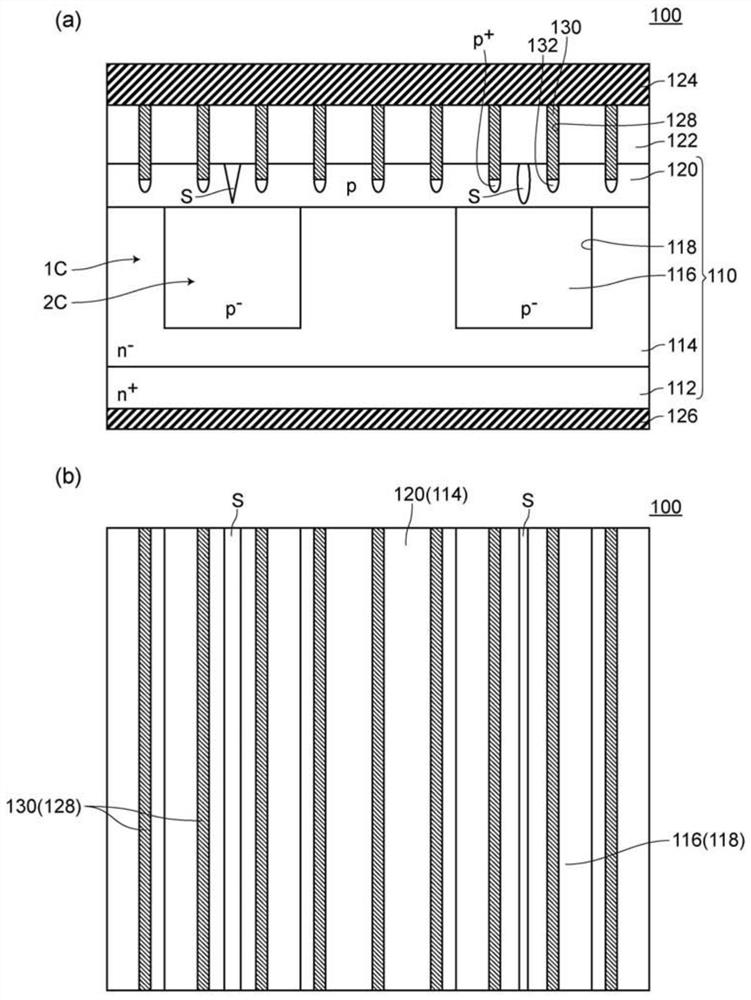

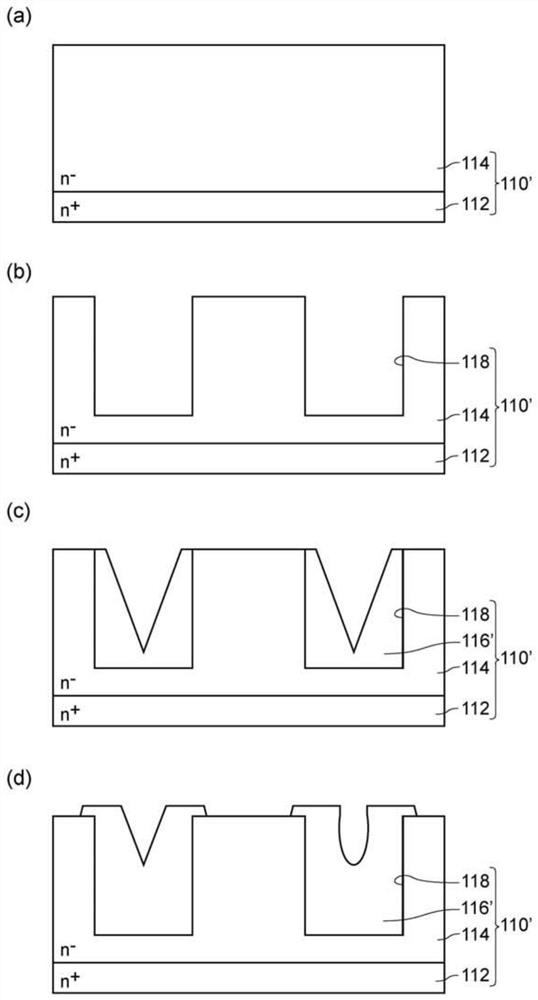

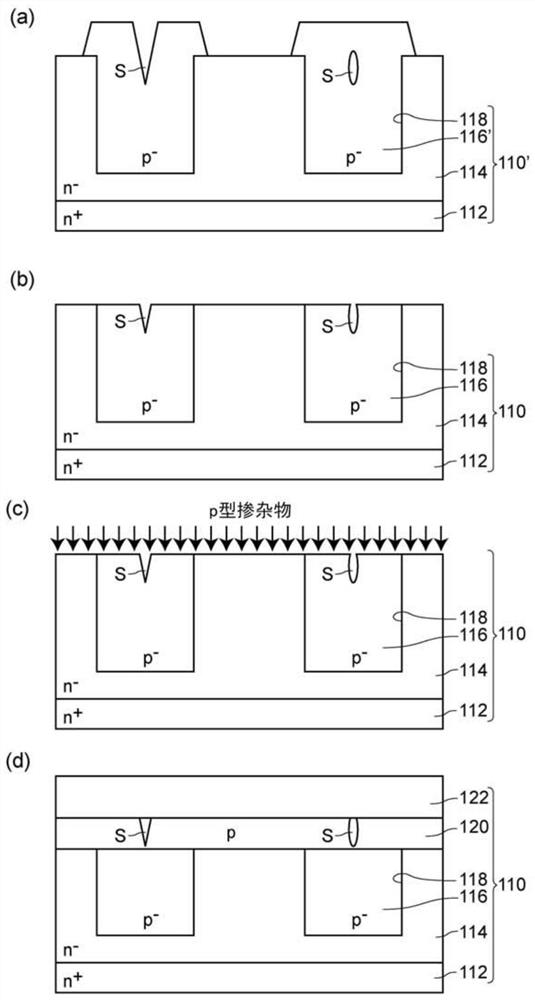

[0067] 1. Configuration of the semiconductor device 100 according to the first embodiment

[0068] The semiconductor device 100 according to Embodiment 1 is, for example, figure 1 As shown, it includes: a semiconductor substrate 110 (the same structure as the semiconductor substrate 710, refer to Figure 22 ), at n + Type first semiconductor layer 112 is stacked with n - type second semiconductor layer 114, and the n - The surface of the second semiconductor layer 114 is formed with a plurality of grooves 118 of a predetermined depth arranged in a predetermined direction, and p - type third semiconductor layer 116; the first electrode 126 is located on the surface of the first semiconductor layer 112; the interlayer insulating film 122 is located on the surfaces of the second semiconductor layer 114 and the third semiconductor layer 116, and has: See the prescribed opening 128 formed at least in the region where the third semiconductor layer 116 is formed; the second elec...

Embodiment approach 2

[0114] The semiconductor device 102 according to the second embodiment basically has the same configuration as the semiconductor device 100 according to the first embodiment, but differs from the semiconductor device 100 according to the first embodiment in that the second electrode is directly connected to the third semiconductor layer. . That is, in the semiconductor device 102 according to the second embodiment, as Figure 7 As shown, the inside of the opening 128 is directly filled with the metal constituting the second electrode 124 , and the second electrode 124 is directly connected to the fourth semiconductor layer 120 . In addition, no barrier metal (not shown) is formed on the inner surface of the opening 128 .

[0115] The opening 128 is formed in the entire area except the central portion of the third semiconductor layer as viewed in plan.

[0116] The method of manufacturing a semiconductor device according to the second embodiment basically has the same configu...

Embodiment approach 3

[0122] The semiconductor device 104 according to the third embodiment basically has the same configuration as the semiconductor device 100 according to the first embodiment, but differs from the semiconductor device 104 according to the first embodiment in that it is not a PIN diode but a Schottky barrier diode. device 100. That is, in the semiconductor device 104 according to the third embodiment, as Figure 8 As shown, the metal plug 130 is a barrier metal, and the second electrode 124 is a Schottky barrier diode connected not only to the third semiconductor layer 116 but also to the second semiconductor layer 114 . Furthermore, in the third embodiment, the p + type high-concentration diffusion region 132 . In addition, on the surface of the third semiconductor layer 116, a p-type diffusion region 120' is formed.

[0123] In the semiconductor device 104 according to the third embodiment, the second semiconductor layer 114 on the portion to be sandwiched by the adjacent tr...

PUM

| Property | Measurement | Unit |

|---|---|---|

| length | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com