Collaborative simulation accelerator based on FPGA and simulation system and method

A co-simulation and accelerator technology, which is applied in the direction of instruments, special data processing applications, electrical digital data processing, etc., can solve the problems of hours, days or even weeks, reduced product market competitiveness, and extended R&D cycle. , to achieve the effect of speeding up the market, shortening the R&D cycle, and making upgrades easy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

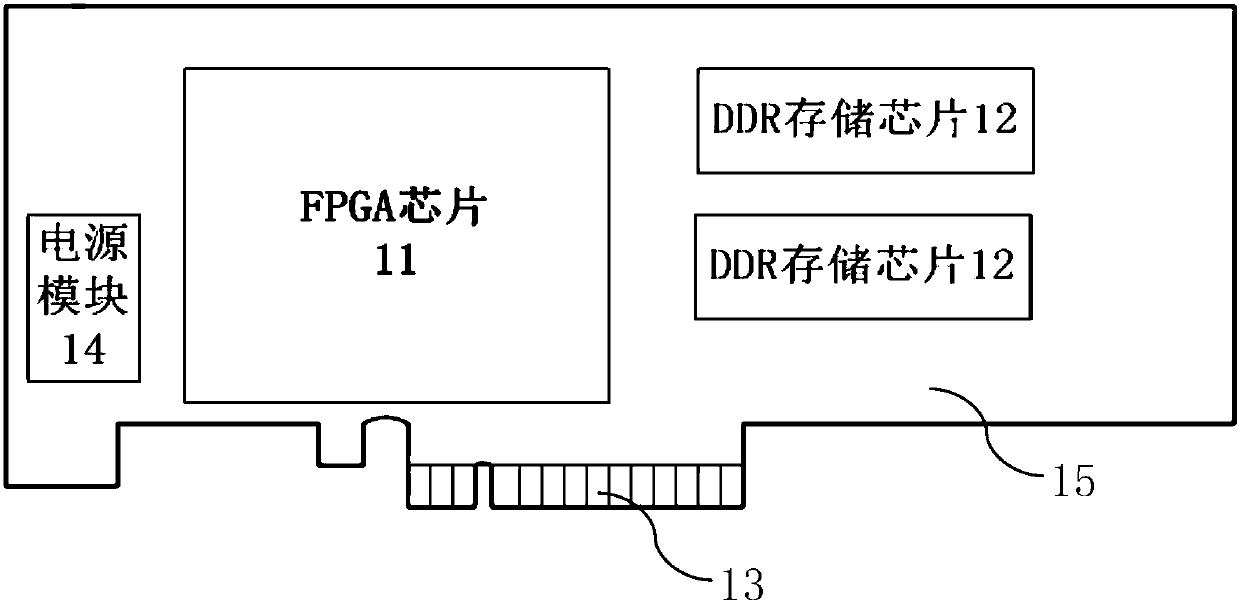

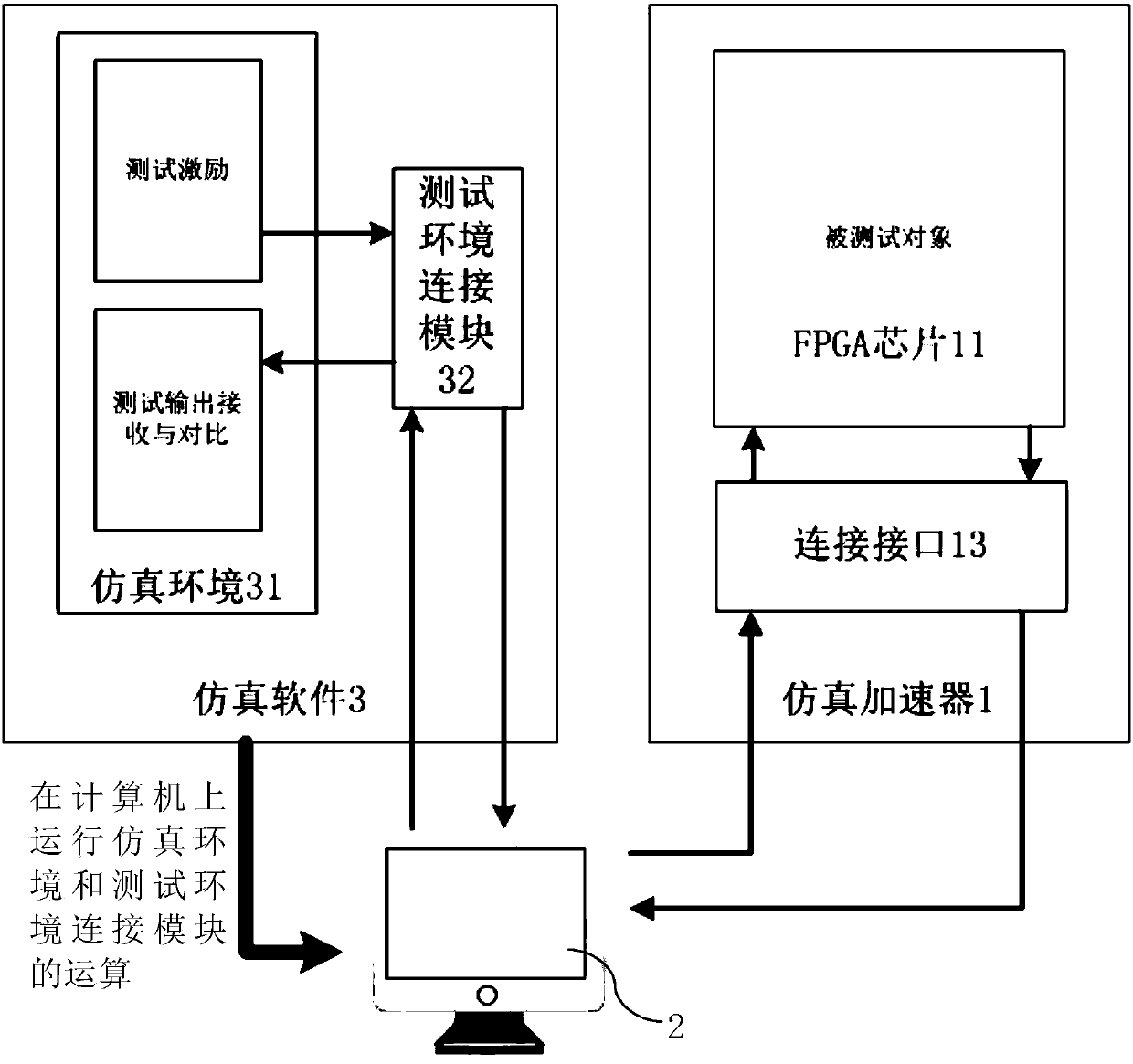

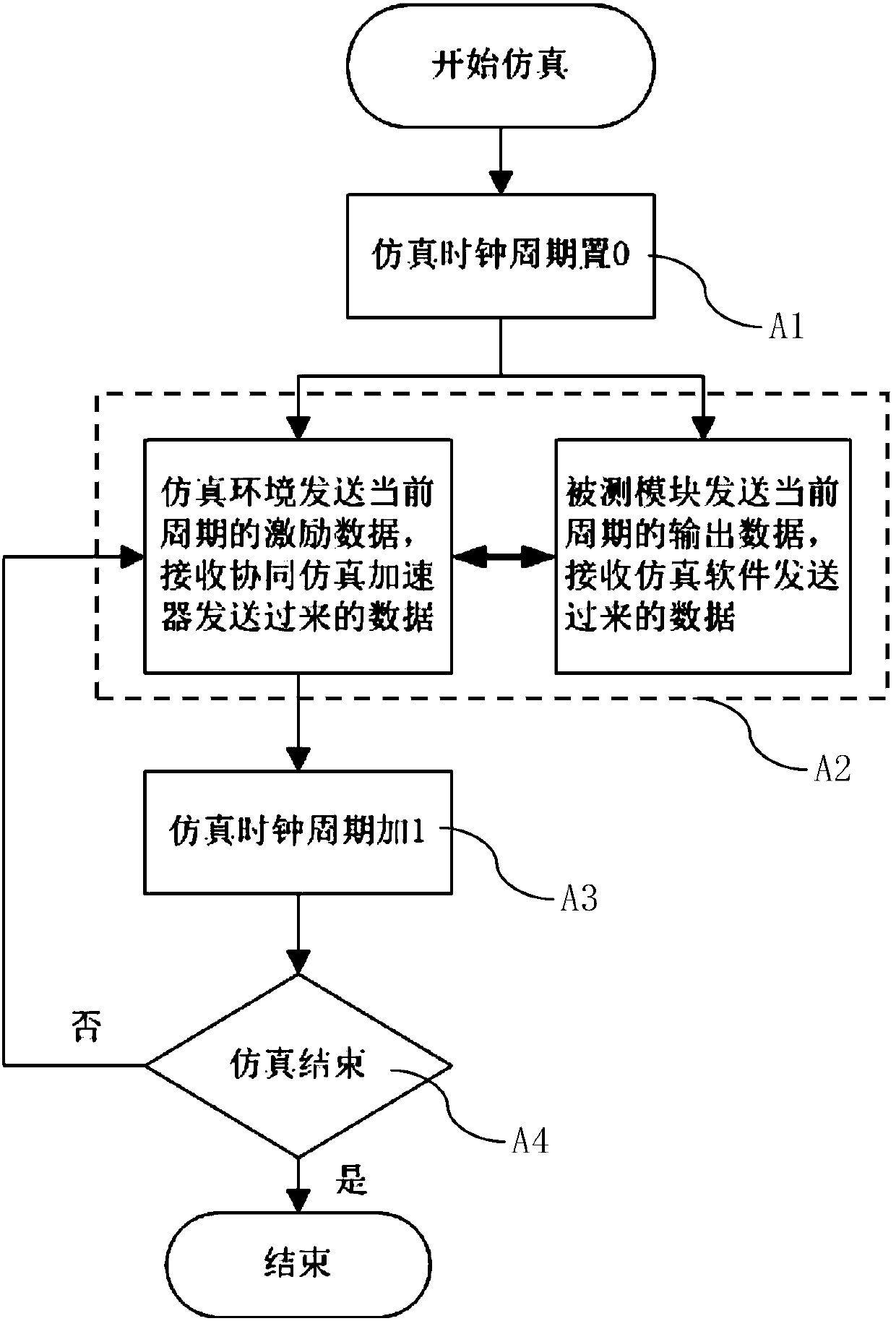

[0027] The embodiment of the present invention provides a kind of co-simulation accelerator based on FPGA, comprises FPGA chip 11, DDR storage chip 12, connection interface 13 and power supply module 14, and described DDR storage chip 12 and connection interface 13 all lead with FPGA chip 11 connected, the input end of the power supply module 14 is electrically connected to the connection interface 13, and the output end is electrically connected to the DDR memory chip 12 and the FPGA chip 11; wherein, the FPGA chip 11 can adopt the Virtex-7 series FPGA chip of Xilinx Company , is mainly used for w...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com