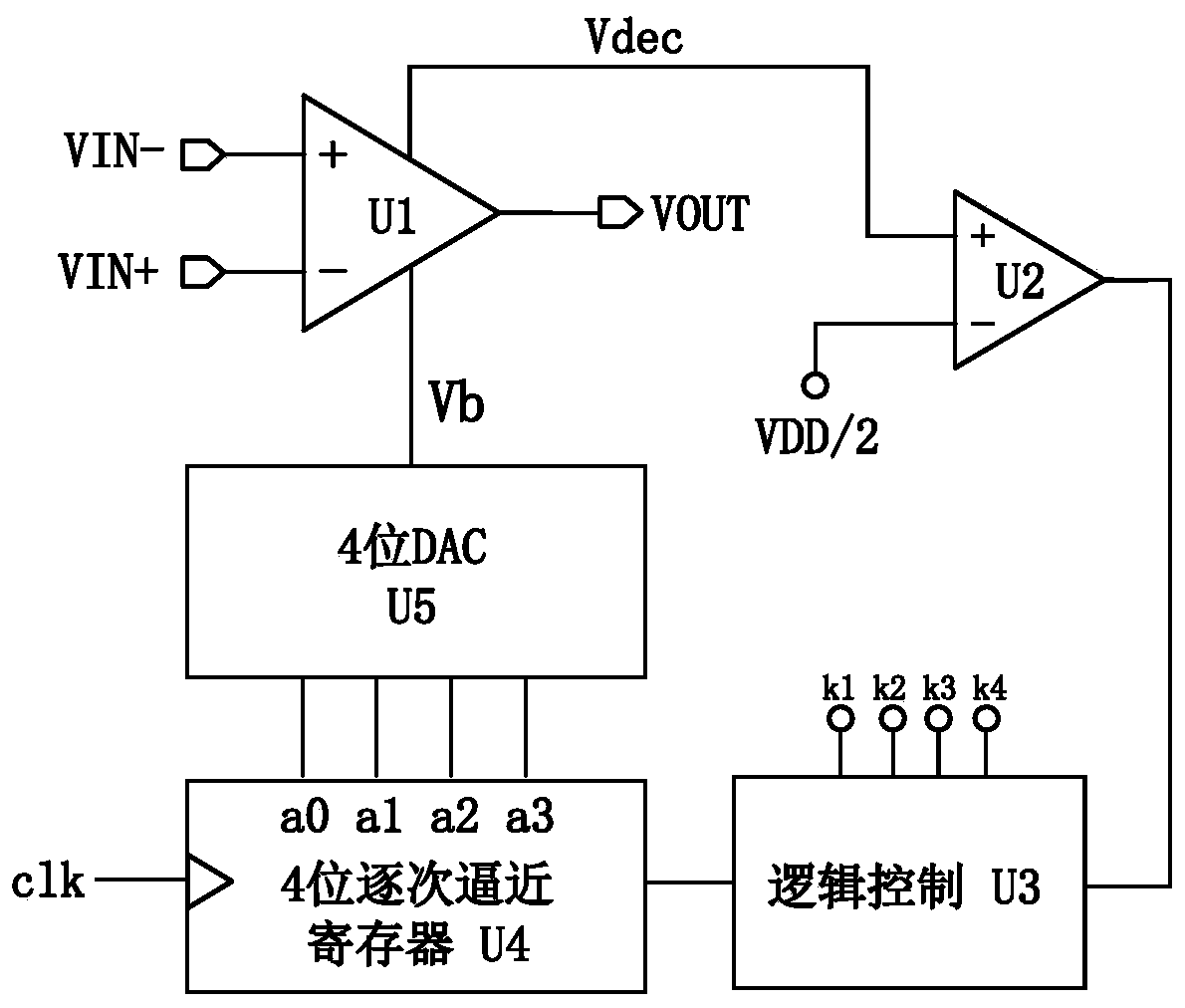

A circuit for correcting operational amplifier offset by successive approximation

A technique of successive approximation and circuit, which is applied in the direction of improving the amplifier to reduce the influence of noise, etc., and can solve the problems of increasing the correction time and long startup time of the op amp

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

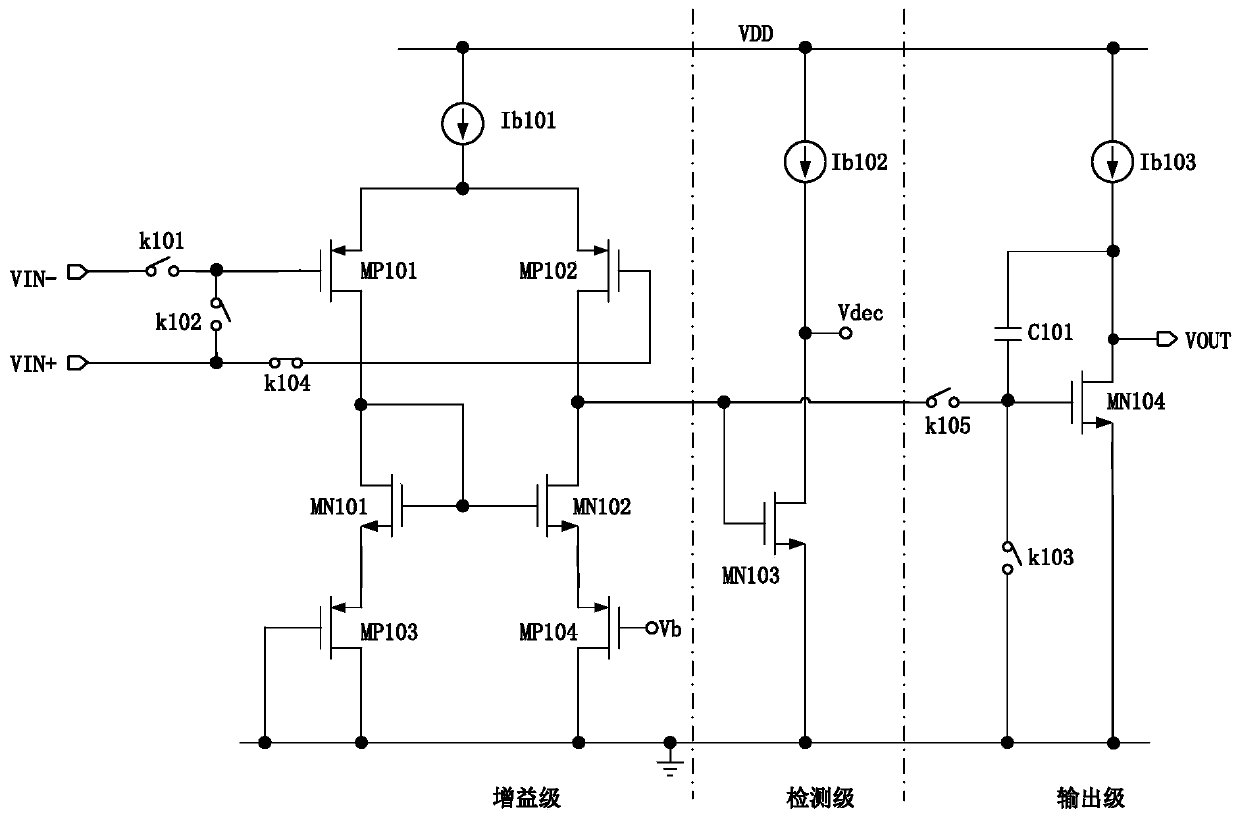

[0024] see figure 2 , is the circuit diagram of the main module of the operational amplifier of the present invention, including PMOS transistor MP101, PMOS transistor MP102, PMOS transistor MP103, PMOS transistor MP104, NMOS transistor MN101, NMOS transistor MN102, NMOS transistor MN103, NMOS transistor MN104, current source Ib101, current source Ib102, current source Ib103, switch k101, switch k102, switch k103, switch k104, switch k105, capacitor C101.

[0025] The operational amplifier is divided into three sections: gain stage, detection stage, and output stage.

[0026] The gain stage includes: PMOS transistor MP101, PMOS transistor MP102, PMOS transistor MP103, PMOS transistor MP104, NMOS transistor MN101, NMOS transistor MN102, current source Ib101, switch k101, switch k102, switch k104. The non-inverting input terminal is connected to the gate of the PMOS transistor MP102 through k104, the inverting input terminal is connected to the gate of the PMOS transistor MP10...

Embodiment 2

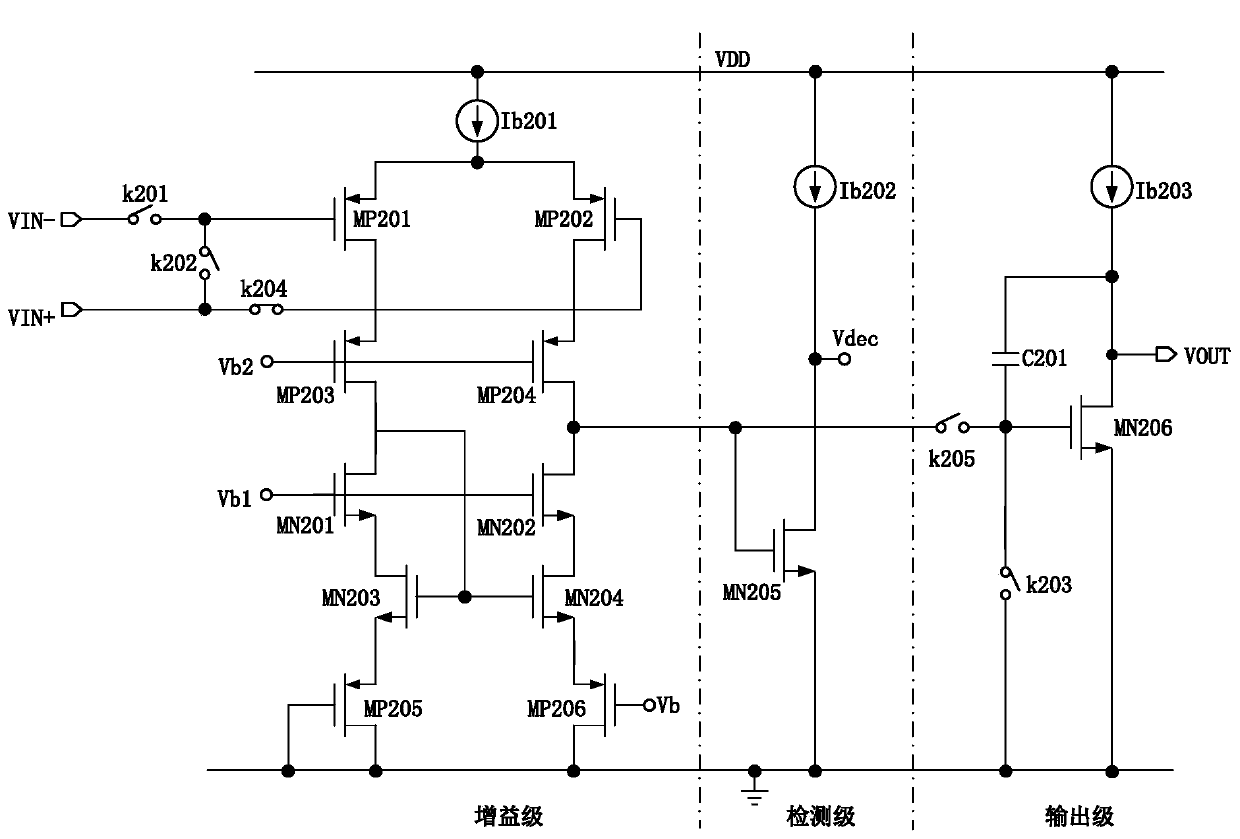

[0036] The structure of the operational amplifier in this embodiment is the same as that in Embodiment 1, and the gain stage in the main module of the operational amplifier is replaced with a telescopic operational amplifier structure.

[0037] see image 3 , is the circuit diagram of the main module of the operational amplifier of the present invention, including PMOS transistor MP201, PMOS transistor MP202, PMOS transistor MP203, PMOS transistor MP204, PMOS transistor MP205, PMOS transistor MP206, NMOS transistor MN201, NMOS transistor MN202, NMOS transistor MN203, NMOS transistor MN204, NMOS transistor MN205, NMOS transistor MN206, current source Ib201, current source Ib202, current source Ib203, switch k201, switch k202, switch k203, switch k204, switch k205, capacitor C201.

[0038] The operational amplifier is divided into three sections: gain stage, detection stage, and output stage.

[0039] The gain stage includes: PMOS transistor MP201, PMOS transistor MP202, PMOS t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com