Integrated circuit fault injection resistant attack ability assessment method based on FPGA (field programmable gate array)

A fault injection, circuit technology, applied in CAD circuit design, electrical digital data processing, special data processing applications, etc., can solve problems such as increasing resource consumption, and achieve the effect of reducing resource consumption and reducing dependencies

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The present invention will be further described below through specific embodiments and accompanying drawings. The embodiments of the present invention are for better understanding of the present invention by those skilled in the art, and do not limit the present invention in any way.

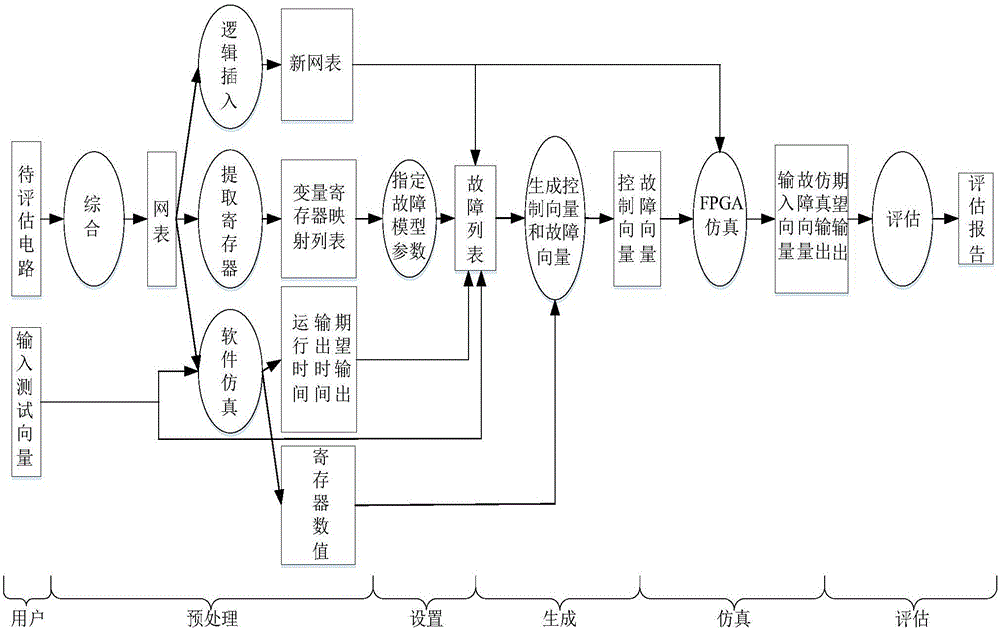

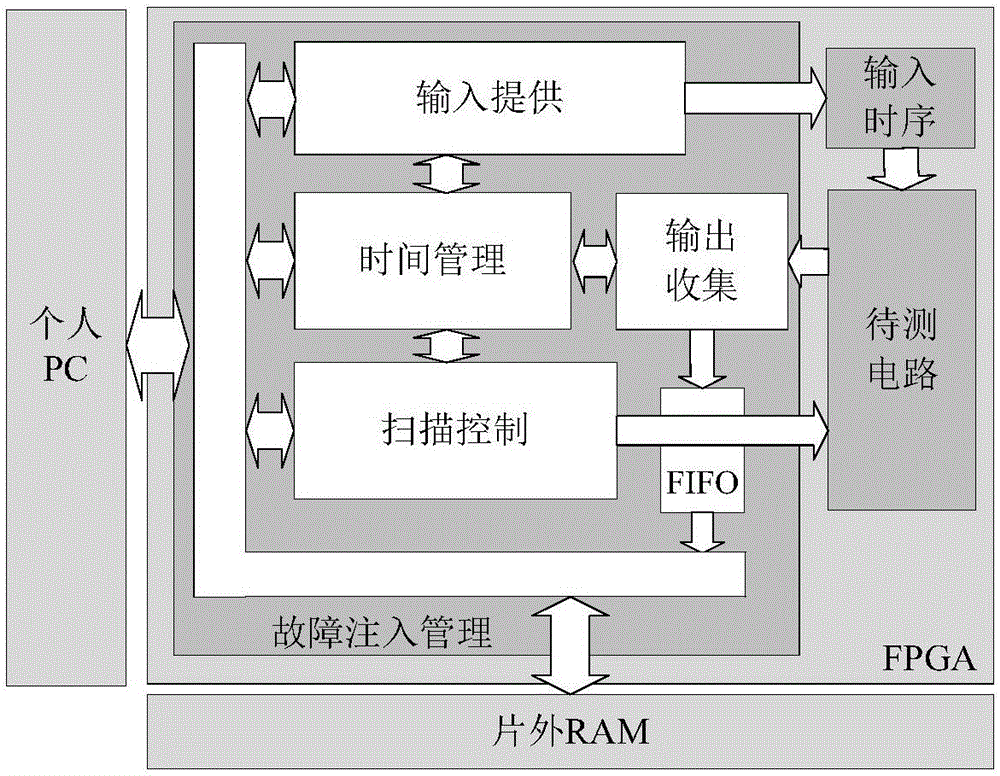

[0028] Such as figure 1 As shown, the method for evaluating the anti-fault injection attack capability of integrated circuits based on FPGA includes the following steps:

[0029] (1), the input of the evaluation device is the source code of the circuit to be evaluated and the list of input vectors;

[0030] (2) Synthesize the source code of the circuit to be evaluated into a netlist, and copy it into three copies for logic insertion, register extraction and software simulation;

[0031] (3), the logic insertion operation inserts the scan chain and the fault injection management module in the netlist, and finally generates a netlist for FPGA simulation;

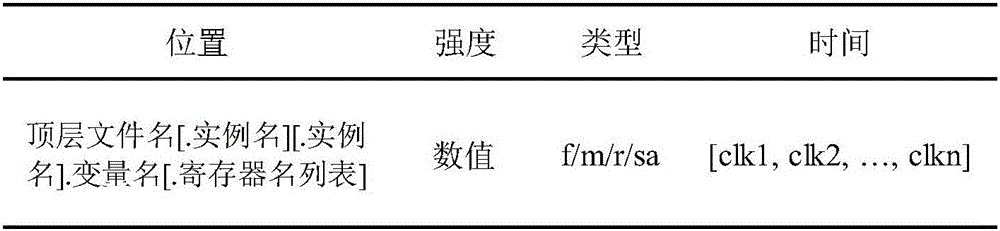

[0032] (4), the operation of ex...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com