Bit stream readback-based FPGA (field programmable gate array) testing platform

A test system and test program technology, applied in the direction of measuring electricity, measuring devices, measuring electrical variables, etc., can solve the problems of slow speed, limited IO number of FPGA chips, increasing the difficulty of FPGA test circuit design and the number of tests, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0014] The present invention will be described in detail below in conjunction with the accompanying drawings.

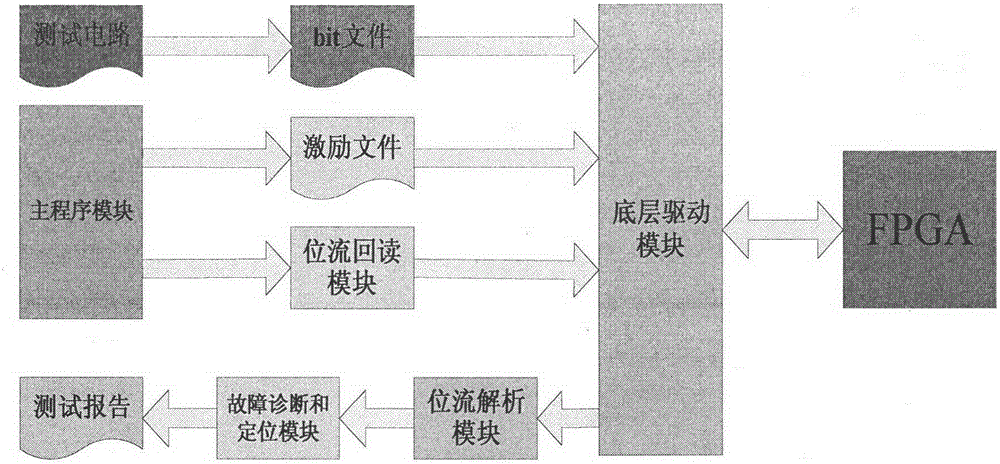

[0015] figure 1 Shown is the FPGA test system architecture diagram. The software part runs in the PC, and the data exchange is completed through the JTAG download cable connected between the USB interface of the PC and the JTAG interface of the FPGA. Therefore, only a JTAG download cable and a PC are needed on the hardware of the FPGA test system for the PC version, and the hardware cost is relatively low.

[0016] figure 2 Shown is the output display when opening the cable is successful. After starting the test, the main program module will first check the connection between the PC and the FPGA device to confirm whether the JTAG cable is working properly. If the JTAG cable is working properly, the program will create a dialog, and at the same time, a message indicating that the cable is successfully opened will be displayed in the display window

[0017] ima...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com