Embedded core wrapper device and design method thereof

An embedded, core-core technology, applied in the field of system-on-chip modular testing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

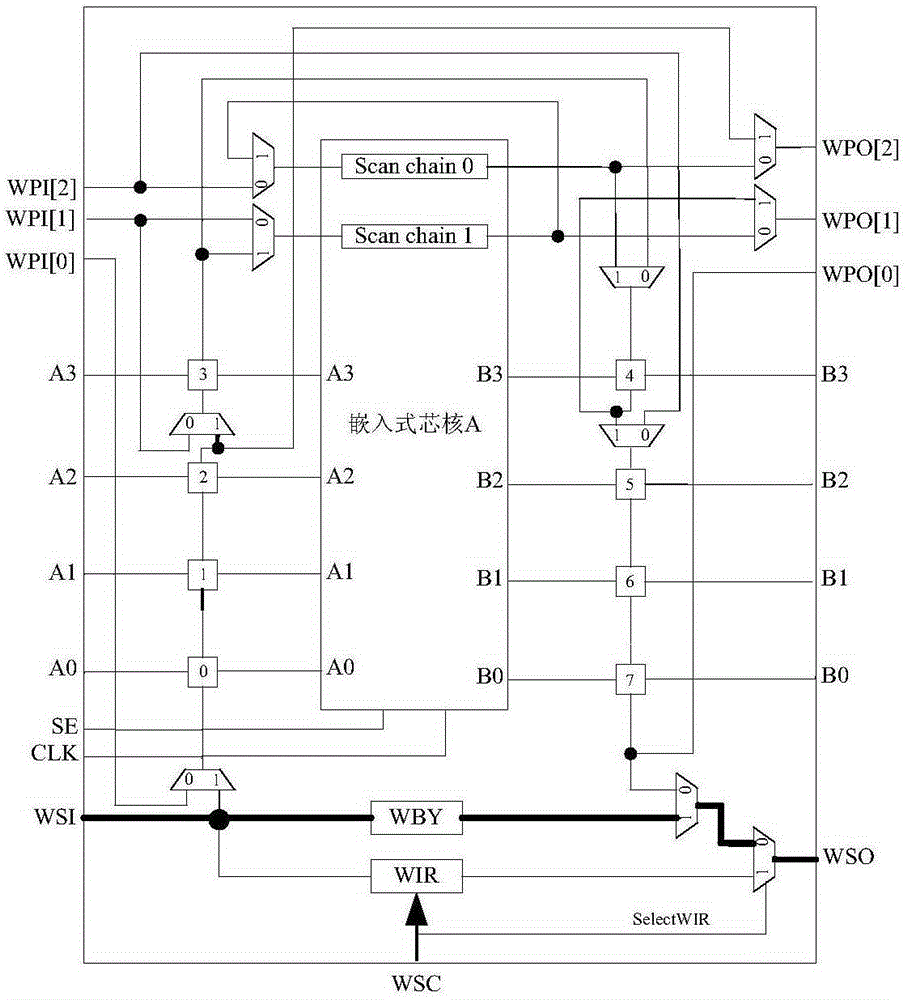

[0065] The core test shell structure stipulated by the IEEEStd1500 standard consists of a test shell boundary register (WrapperBoundaryRegister, WBR), a test shell bypass register (WrapperBypassRegister, WBY), a test shell instruction register (WrapperInstructionRegister, WIR), a test shell serial port (WrapperSerialPort, WSP ) and an optional test shell parallel port (WrapperParallelPort, WPP).

[0066] Among them, WBR is a data register, which is used to provide test stimulus and receive test response. WBR is composed of serially connected test shell boundary register unit (WBRCell). WBRCell can realize the application of test stimulus and capture of test response, so as to realize the control and observation of the embedded core. Each input and output port of the embedded core has a WBRCell, but the test access mechanism (TestAccessMechanism, TAM) port and the analog port may not be provided with a WBRCell. IEEEStd1500 only defines two types of WBRCell: input WBRCell and o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com