High-precision successive approximation type analog-digital converter and performance lifting method based on DNL (dynamic noise limiter)

一种模数转换器、逐次逼近型的技术,应用在模/数转换、代码转换、仪器等方向,能够解决补偿电容阵列很难实现等问题,达到节省版图面积和功耗、提高测量和校正精度、实现数字校正的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0082] In order to make the technical means, creative features, goals and effects achieved by the present invention easy to understand, the present invention will be further described below in conjunction with specific illustrations.

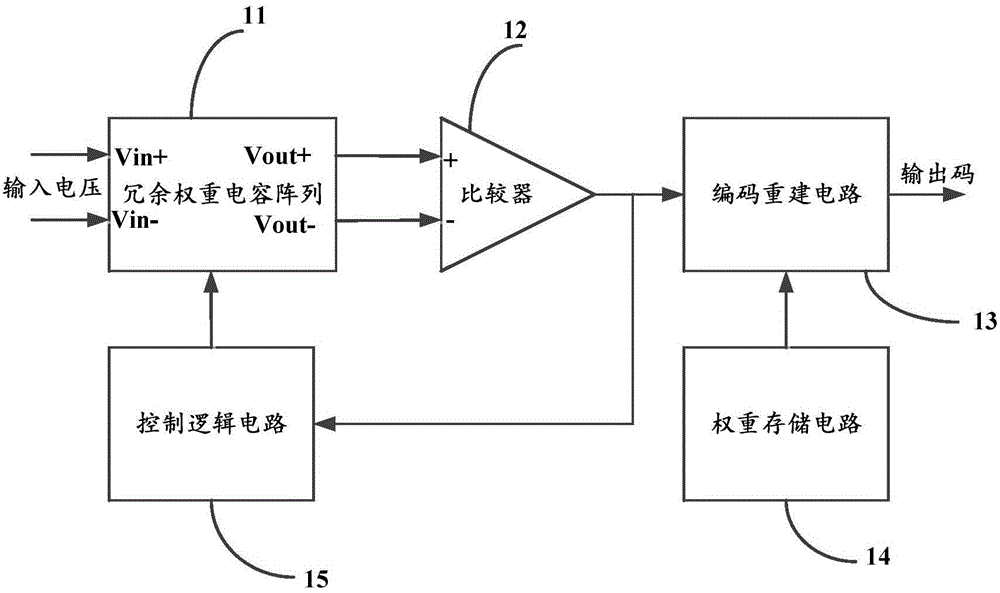

[0083] Please refer to figure 1 As shown, the present invention provides a high-precision successive approximation analog-to-digital converter, including a redundant weight capacitor array 11, a comparator 12, a code reconstruction circuit 13, a weight storage circuit 14 and a control logic circuit 15; wherein,

[0084] The redundant weight capacitor array 11 receives external input voltages Vin+ and Vin-, and under the control of the control logic circuit 15, generates output voltages Vout+ and Vout-, which are sent to the comparator 12 for comparison. According to the comparator 12 comparison results, under the control of the control logic circuit 15, sequentially control each capacitor to participate in the voltage addition and subtraction op...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com