Multi-core DMA (direct memory access) subsection data transmission method used for GPDSP and adopting host counting

A segmented data and transmission method technology, applied in the direction of electrical digital data processing, instruments, etc., can solve the problems of limited data transmission efficiency, small bit width, calculation accuracy and insufficient addressing space, and achieve effective perception of memory access characteristics, Effect of load reduction and on-chip network load reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

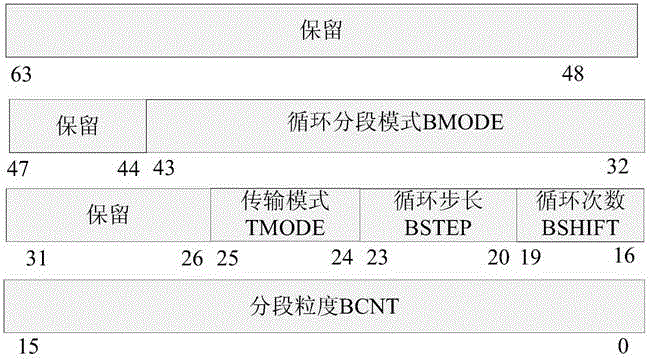

[0039] Such as figure 1 Shown is a schematic diagram of the GPDSP architecture of the method of the present invention in a specific application example. The multi-core GPDSP processor is composed of DSP nodes, on-chip network and DDR3SDRAM outside the core. Each DSP node includes a DSP core, and the network-on-chip implements data communication between each DSP node and between the DSP node and an external storage unit. Such as figure 2 Shown is a schematic diagram of the location of the DMA in the GPDSP calculation kernel in this embodiment. DMA is connected with components such as peripheral hardware configuration bus (PBUS), vector memory (Vector Memory, VM) and scalar memory (Scalar Memory, SM) in the DSP core. Among them, the scalar processing unit SPU configures transmission parameters for the DMA unit through the periphera...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com