ROM read data internal clock pulse generation circuit and method

An internal clock and circuit generation technology, applied in read-only memory, information storage, static memory, etc., can solve the problems of ROM reading speed slowdown, ROM power consumption increase, etc., to reduce ROM power consumption and read time, The effect of reducing the payload size

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

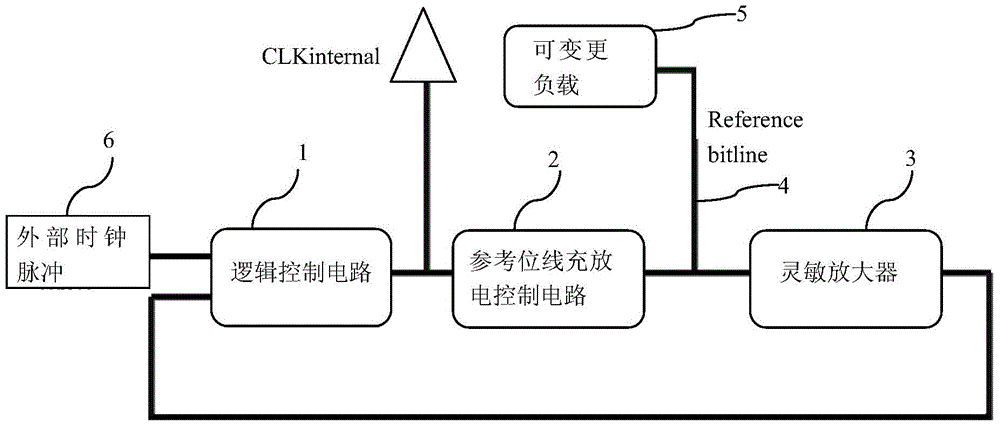

[0031] Such as image 3 What is described is a schematic diagram of the internal clock pulse generating circuit for ROM reading data in the embodiment of the present invention; the internal clock pulse generating circuit for ROM reading data in the embodiment of the present invention includes: logic control circuit 1, reference bit line 4 charge and discharge control circuit 2, and sensitive amplifier circuit 3. The reference bitline is Reference bitline4;

[0032] The load of the reference bit line 4 is a changeable load 5, and the changeable load 5 is adjusted according to the maximum bit line load in the ROM circuit after the ROM data code is written into the ROM circuit.

[0033] The reference bit line 4 charge and discharge control circuit 2 is used to charge and discharge the reference bit line 4 and obtain a charge and discharge time, and the charge and discharge time is determined by the variable load 5.

[0034] The sensitive amplifying circuit 3 and the logic control circui...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com