A method of fpga interactive simulation based on tcl

A simulation method, interactive technology, applied in the direction of software testing/debugging, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

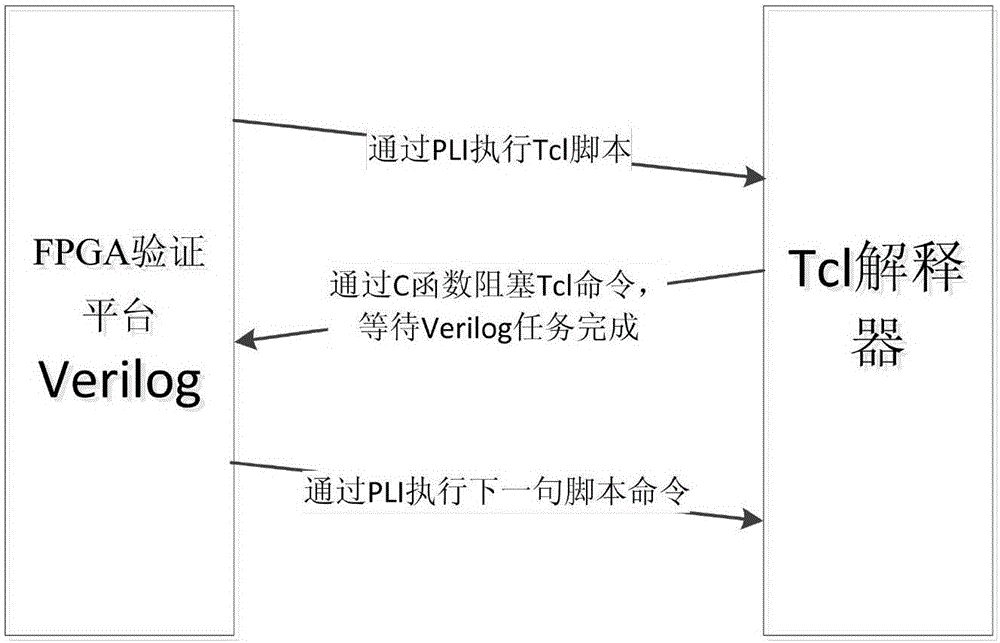

[0018] The TCL_PLI library allows any Tcl statement to be called in the verilog simulation. The function of PLI is to initialize the Tcl interpreter and map the Tcl function to the verilog task. In addition, it can also help start the script in the Tcl interpreter. Control the interaction between verilog and Tcl. Verilog's task has an entry that allows Tcl to pass variables to Verilog. Similarly, Verilog can also pass returned variables to Tcl. PLI provides this kind of information sharing and data transfer between Tcl and verilog.

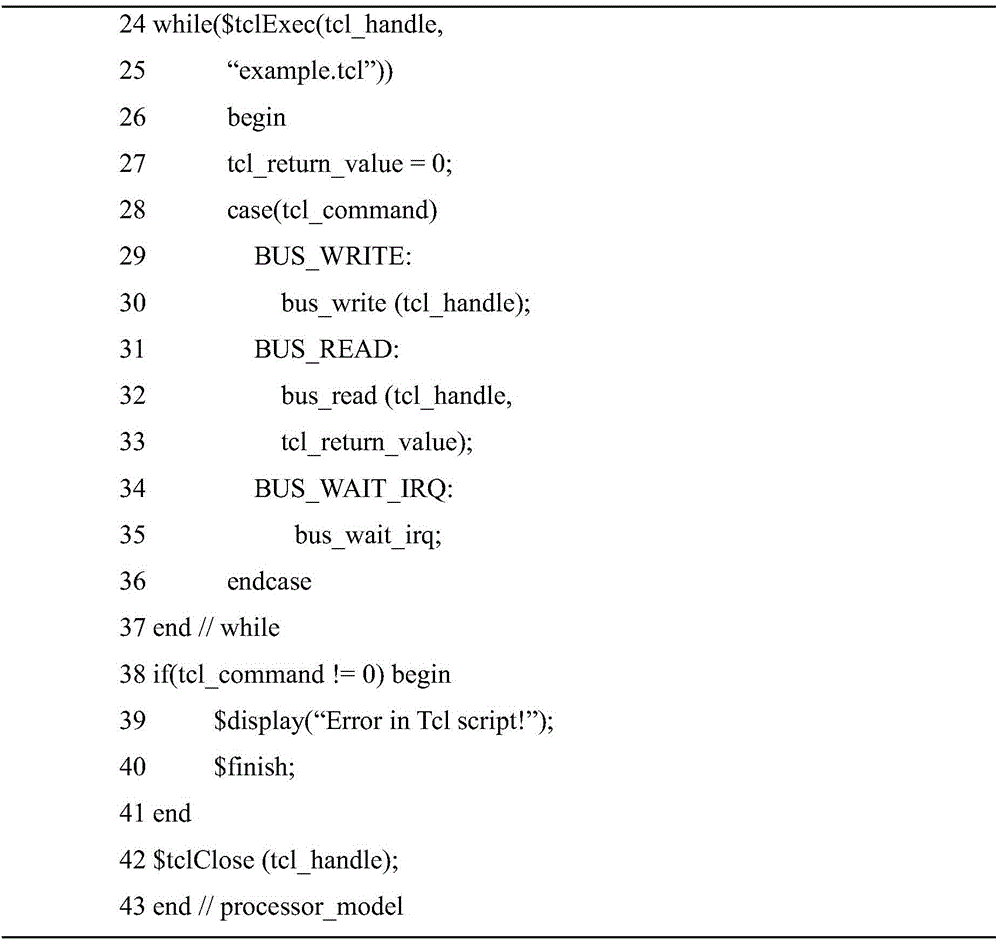

[0019] There are four PLI functions in the TCL_PLI library: $tcllnit, $tclExec, $tclGetArgs, and $tclClose. $tcllnit is used to create and initialize a new Tcl interpreter. It defines a new Tclfunction that can be called by Verilog's task and is mapped to the corresponding task. It also defines how many parameters can be used. $tclExec is used to execute a new script to map Tcl commands to Verilog tasks. $tclGetArgs is used to get the parameter v...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com