High-speed cache block length adjusting method and device of high-speed cache memory

A high-speed cache and cache technology, applied in the computer field, can solve the problem that the length of the cacheline cannot be changed and adjusted, and achieve the effect of increasing the access rate and improving the system performance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

example 1

[0049] Example 1, Table 1 is the cache structure of the cacheline with a length of 32 bytes, and n=5 at this time;

[0050] Table 1

[0051]

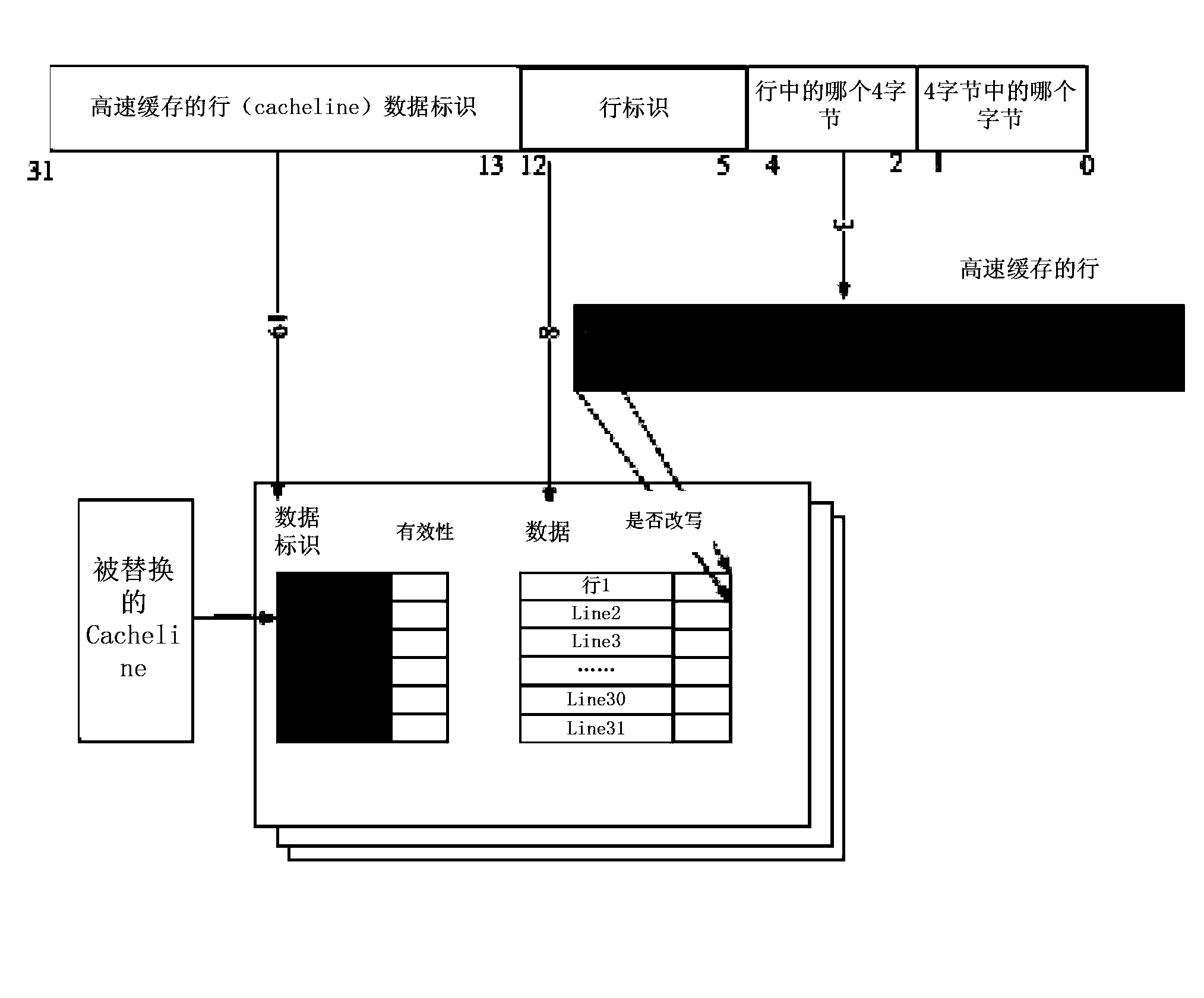

[0052] image 3 It is a schematic diagram of a cache structure of a cacheline with a length of 32 bytes in an embodiment of the present invention, such as image 3 As shown, if the Cache size is 32k bytes, 32 sets are used. When the cacheline size is 32bytes, then each Set has 32 cachelines, that is, 32ways. If the starting address is 0x0, then way0 stores 0x00000000~0x000003ff; way1 stores 0x00000400~0x7ff; ..., Way31 stores 0x7c00~0x7fff. Among them, bit[31:13] indicates the first address of the way where the set is located, bit[12:5] indicates which cacheline it is, and bit[4:2] indicates the offset address of the word in the cacheline.

example 2

[0053] Example 2, table 2 is the structure of 64bytes cacheline length, n=6 at this time;

[0054] Table 2

[0055]

[0056] Figure 4 It is a schematic diagram of the cache structure of a cacheline with a length of 64 bytes in the embodiment of the present invention. In the cache, a set associative method is adopted to design the cache. If the Cache size is 32k bytes, then 32 sets are used. When the cacheline size is 64byte, then Each Set has 16 cachelines, that is, 32 ways. If the starting address is 0x0, then way0 stores 0x00000000~0x000003ff; way1 stores 0x00000400~0x7ff; ...; Way31 stores 0x7c00~0x7fff. Among them, bit[31:14] indicates the first address of the group (Set) t where the set is located, bit[15:6] indicates which cacheline it is, and bit[5:2] indicates the offset address of the word in the cacheline.

[0057] According to Example 1 and Example 2, the structural composition of the cache of other cacheline sizes can be obtained.

[0058] 2. The operation t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com