A method for manufacturing a silicon-germanium heterojunction bipolar transistor

A technology of heterojunction bipolar and manufacturing method, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of SiGeHBT performance deterioration, external expansion, etc., to avoid re-diffusion, good device performance, prevent The Effect of Heterojunction Barrier Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0031] A method for manufacturing a germanium-silicon heterojunction bipolar transistor of the present invention comprises the following steps:

[0032] Step S01 , forming an N+ buried layer region in the silicon substrate, and forming an N− collector region on the N+ buried layer region.

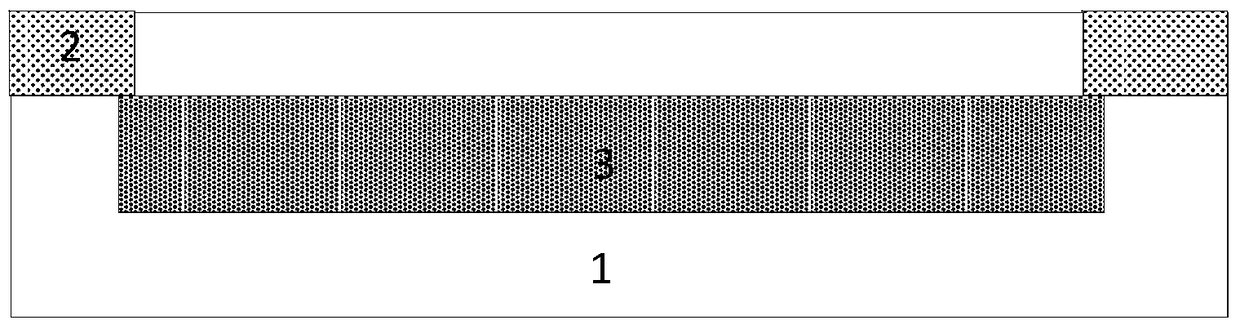

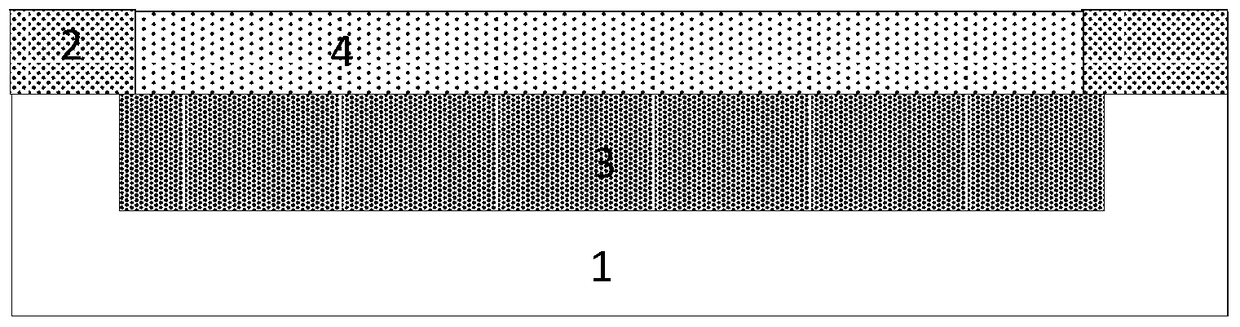

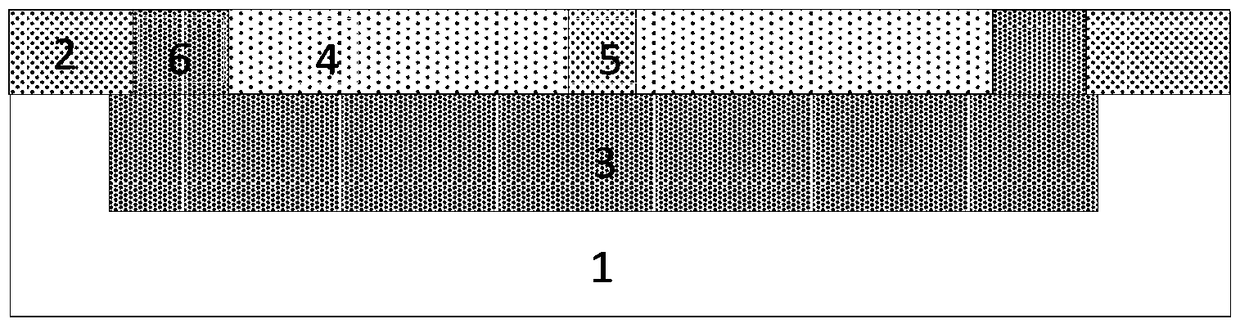

[0033] see figure 1 and figure 2 Specifically, forming the N+ buried layer region 3 in the silicon substrate 1 includes: depositing a layer of first SiO on the silicon substrate 1 2 Layer 2: Etching the above-mentioned first SiO by dry etching and / or wet etching 2 layer 2 until the upper surface of the silicon substrate 1, in the first SiO 2 Form the window of N+ buried layer region 3 in layer 2; then ion-implant N-type impurities and anneal in a high-temperature furnace to obtain N+ buried layer region 3 located in silicon substrate 1, wherein the above-mentioned N-type impurities are phosphorus or arsenic or antimony . In this embodiment, the aforementioned silicon substrate 1 is a...

Embodiment 2

[0051] A method for manufacturing a germanium-silicon heterojunction bipolar transistor of the present invention comprises the following steps:

[0052] Step S01 , forming an N+ buried layer region in the silicon substrate, and forming an N− collector region on the N+ buried layer region.

[0053] see figure 1 with figure 2 Specifically, forming the N+ buried layer region 3 in the silicon substrate 1 includes: depositing a layer of first SiO on the silicon substrate 1 2 Layer 2: Etching the above-mentioned first SiO by dry etching and / or wet etching 2 layer 2 until the upper surface of the silicon substrate 1, in the first SiO 2 Form the window of N+ buried layer region 3 in layer 2; then ion-implant N-type impurities and anneal in a high-temperature furnace to obtain N+ buried layer region 3 located in silicon substrate 1, wherein the above-mentioned N-type impurities are phosphorus or arsenic or antimony . In this embodiment, the aforementioned silicon substrate 1 is ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com