Sampling device for timing analysis of logic analyzer

A logic analyzer and timing analysis technology, which is applied in the field of signal testing devices for the forward channel of the logic analyzer, can solve the problems of memory access speed limitation, difficult and stable realization of SRAM, etc., and achieves the effect of improving reliability.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

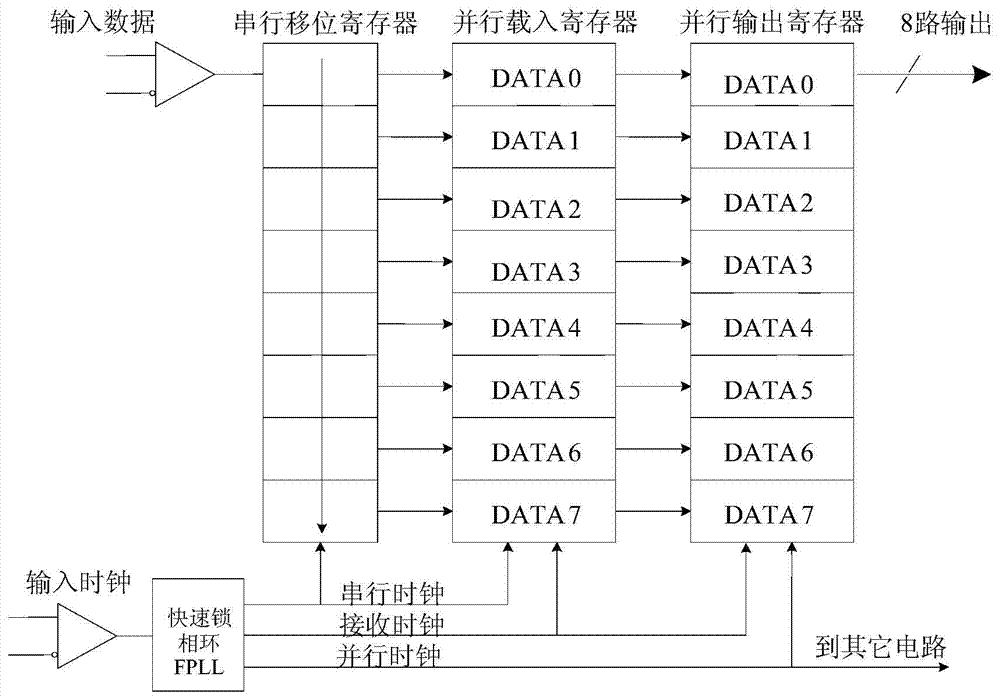

[0011] The sampling device for logic analyzer timing analysis of the present invention includes a shift register, a high-speed differential interface, a parallel latch module, a high-speed clock, and a low-speed clock. The memory module and the low-speed clock are connected, and the high-speed clock and the low-speed clock are connected through a frequency divider.

[0012] The high-speed differential interface includes a serial shift register, a parallel load register, a parallel output register, and a fast phase-locked loop FPLL. The serial shift register is connected to the parallel load register, and the parallel load register is connected to the parallel output register. The phase loop FPLL is respectively connected with the serial shift register and the parallel load register through the serial clock, and the fast phase-locked loop FPLL is respectively connected with the parallel load register and the parallel output register through the receiving clock, and the fast phas...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com