Parametric universal FIFO control method

A control method and parameterized technology, applied in data conversion, electrical digital data processing, instruments, etc., can solve the problems of resource waste, hidden danger of metastability, loss of Gray code, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

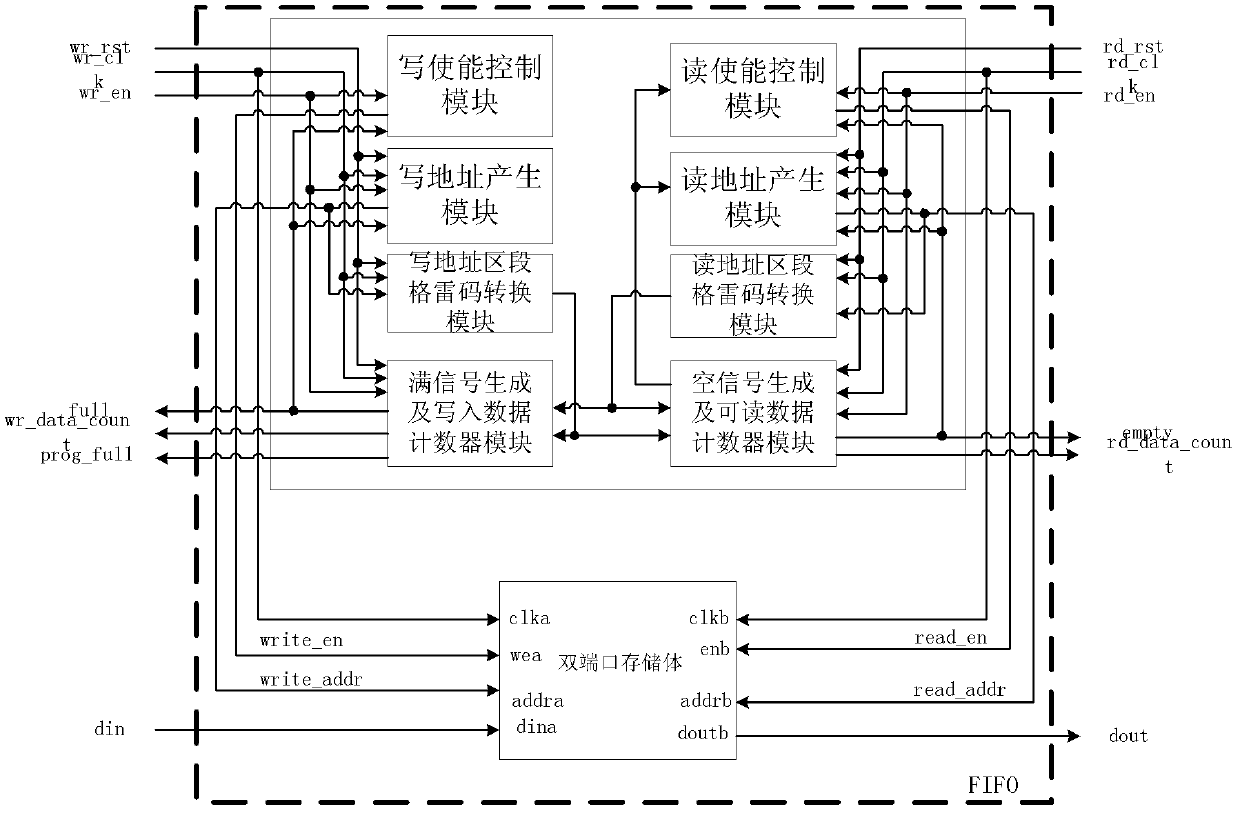

[0075]The parameterized general-purpose FIFO control circuit and implementation method disclosed in the present invention can realize internal address generation, read-write pointers necessary for synchronous FIFO or asynchronous FIFO according to preset static input parameters such as depth and programming full threshold by means of pre-compilation. Control circuit, empty and full sign and other control circuits can be connected to the corresponding dual-port memory externally to form a FIFO that completes the function.

[0076] This circuit structure and implementation method can realize synchronous FIFO or asynchronous FIFO necessary internal address generation, read and write pointer control, empty and full flag, etc. in addition to the storage body by means of pre-compilation, according to the preset static input parameters such as depth and programming full threshold. all control circuits.

[0077] The static input parameters of the parameterized general-purpose FIFO con...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com