Charge pump circuit of EEPROM (Electrically Erasable Programmable Read-Only Memory) used for passive UHF RFID (Ultra High Frequency Radio Frequency Identification Device) chip

A charge pump and circuit technology, applied in the field of microelectronics, can solve the problems of increasing chip area or power consumption, not meeting the application requirements of passive ultra-high frequency radio frequency identification UHFRFID, etc., to reduce peak power consumption and total power consumption, meet the The effect of application requirements

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] The present invention will be described in detail below in conjunction with the accompanying drawings and examples.

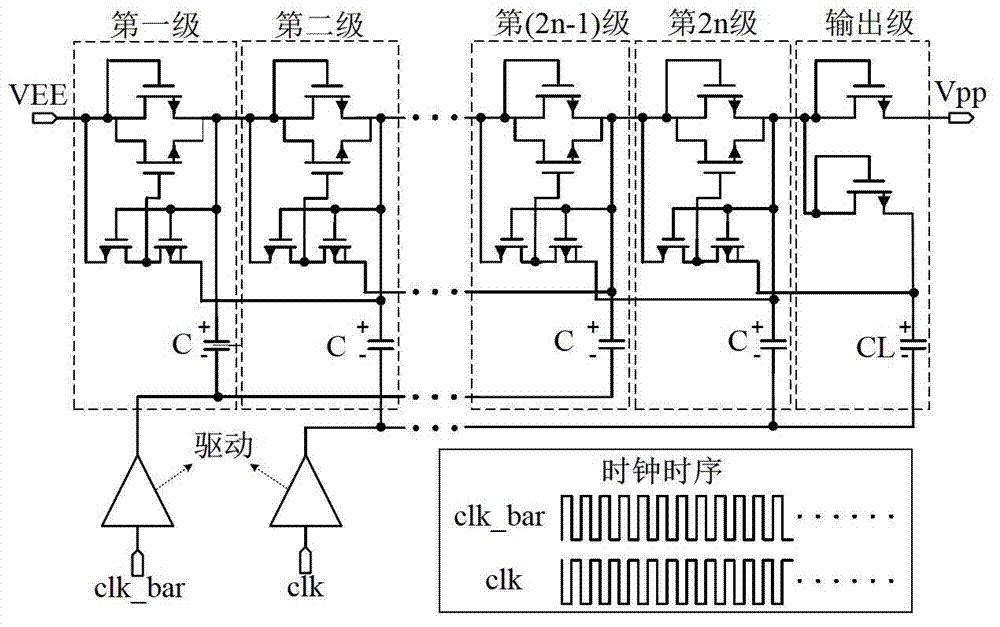

[0033] refer to figure 1 , the traditional CTS charge pump consists of 2n stages of the same CTS charge pump unit and the output stage in series, wherein: the charge pump units of odd stages are connected to the first non-overlapping clock signal clk_bar at the same time, and the charge pump units of even stages are connected to the second non-overlapping clock signal at the same time. Overlapping clock signal clk. After the CTS charge pump starts to work, the bidirectional non-overlapping clock signals clk_bar and clk are valid at the same time, and each stage of the CTS charge pump starts to work at the same time. Therefore, during the power-on period of the charge pump circuit, all capacitors in the circuit, including parasitic Capacitor charging, and the sum of these capacitors will exceed 30pF. To fully charge a large capacitor of about 30pF in a s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com