Synchronization method for single carrier frequency domain equalization system and realization circuit thereof

A single-carrier frequency domain, equalization system technology, applied in multi-frequency code systems, baseband system components, shaping networks in transmitters/receivers, etc., can solve signal timing drift, decision interference, and affect the performance of synchronization, etc. problem, to achieve the effect of concise and concise frame structure, lightening the burden, and improving the data transmission rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] specific implementation plan

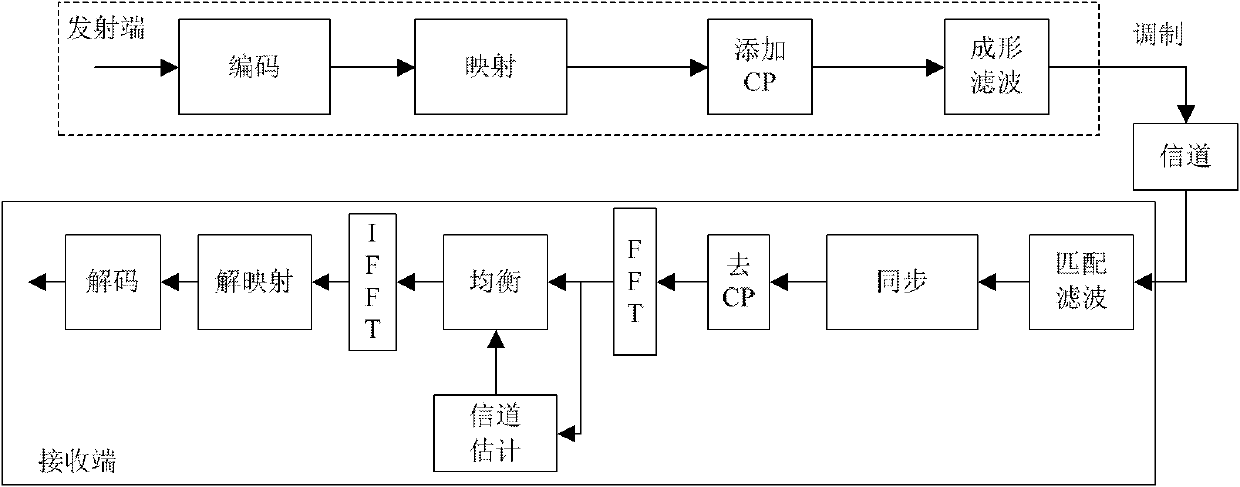

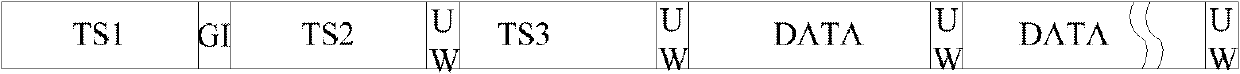

[0028] A synchronization method in a single carrier frequency domain equalization (SC-FDE) system, which divides the preamble of the frame structure in the single carrier frequency domain equalization system into three training sequences TS1, TS2 and TS3;

[0029] Each training sequence is composed of different training words, which is a sequence known by both the sending end and the receiving end. It is less affected by noise and frequency offset, that is, frequency offset, and is suitable for synchronization and channel estimation algorithms;

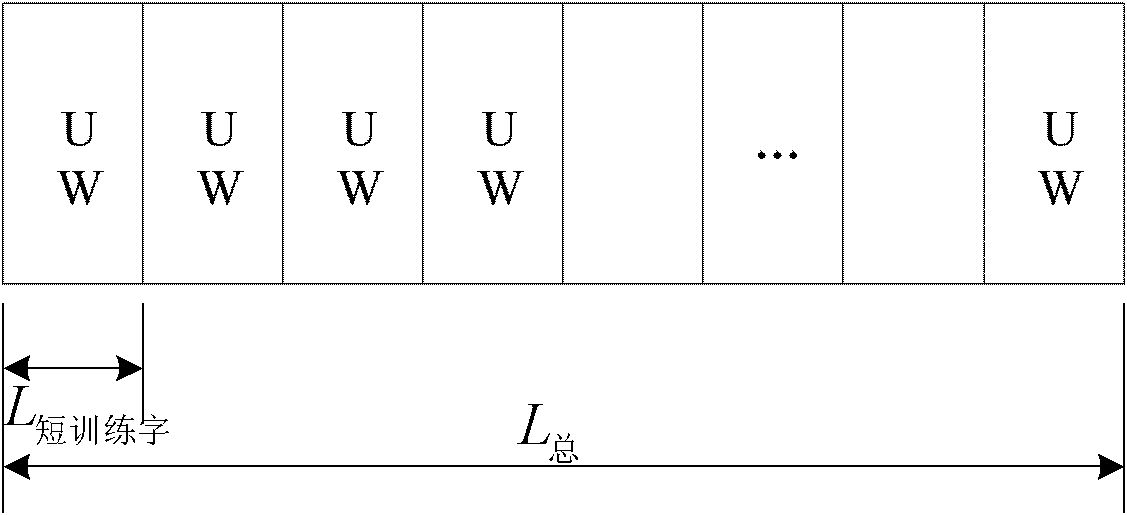

[0030] The first training sequence TS1 is composed of a series of repeated short training words UW, which is used for frame arrival detection, coarse sampling synchronization and coarse carrier frequency offset estimation; the second training sequence TS2 is used for bit synchronization; the third training sequence TS3 consists of two identical training words for fine carrier frequency offset esti...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com