Circuit for improving IO speed

A circuit and speed technology, applied in the field of IO circuits, can solve the problems of long level rise time, long communication time, low data output rate, etc., and achieve the effect of improving communication efficiency, shortening communication time, and improving data transmission speed.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

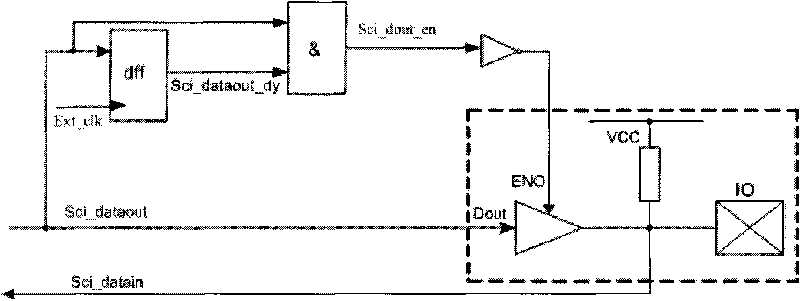

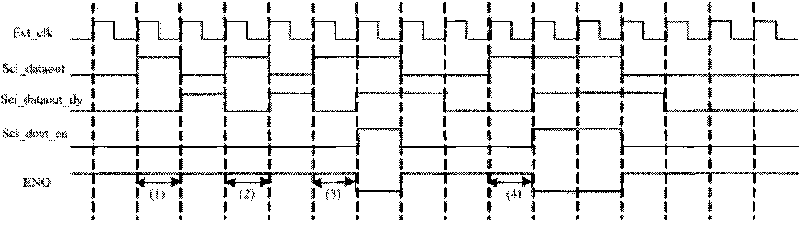

[0011] refer to figure 2 As shown, the open-drain structure proposed by the present invention adds an accelerated conversion pulse of one clock cycle during the "0-1" level conversion, and an IO circuit structure with a pull-up resistor and a tri-state transmission gate structure, including a tri-state bidirectional open-drain IO PAD, a group of logic gate circuits that generate a three-state gate enable signal (ENO).

[0012] The serial port output data (Sci_dataout) is locked by a D flip-flop (using the serial port working clock Ext_clk) to generate the Sci_dataout_dy signal. After this signal and the original serial port output data pass through the AND gate, the serial port output data enable signal (Sci_dout_en) is generated. Thus, the serial port data enable signal passes through a NOT gate to generate an enable signal, which is the enable terminal (ENO) signal of the tri-state gate. The three-state gate enable signal ENO generated according to this circuit structure h...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com