Structure with compatibility of I2C and system management buses and time sequence buffering mechanism

A system management bus and buffer device technology, applied in the direction of electrical digital data processing, instruments, etc., can solve the problem of inconsistent data retention time, and achieve the effect of overcoming the interference of load capacitance and signal reflection.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

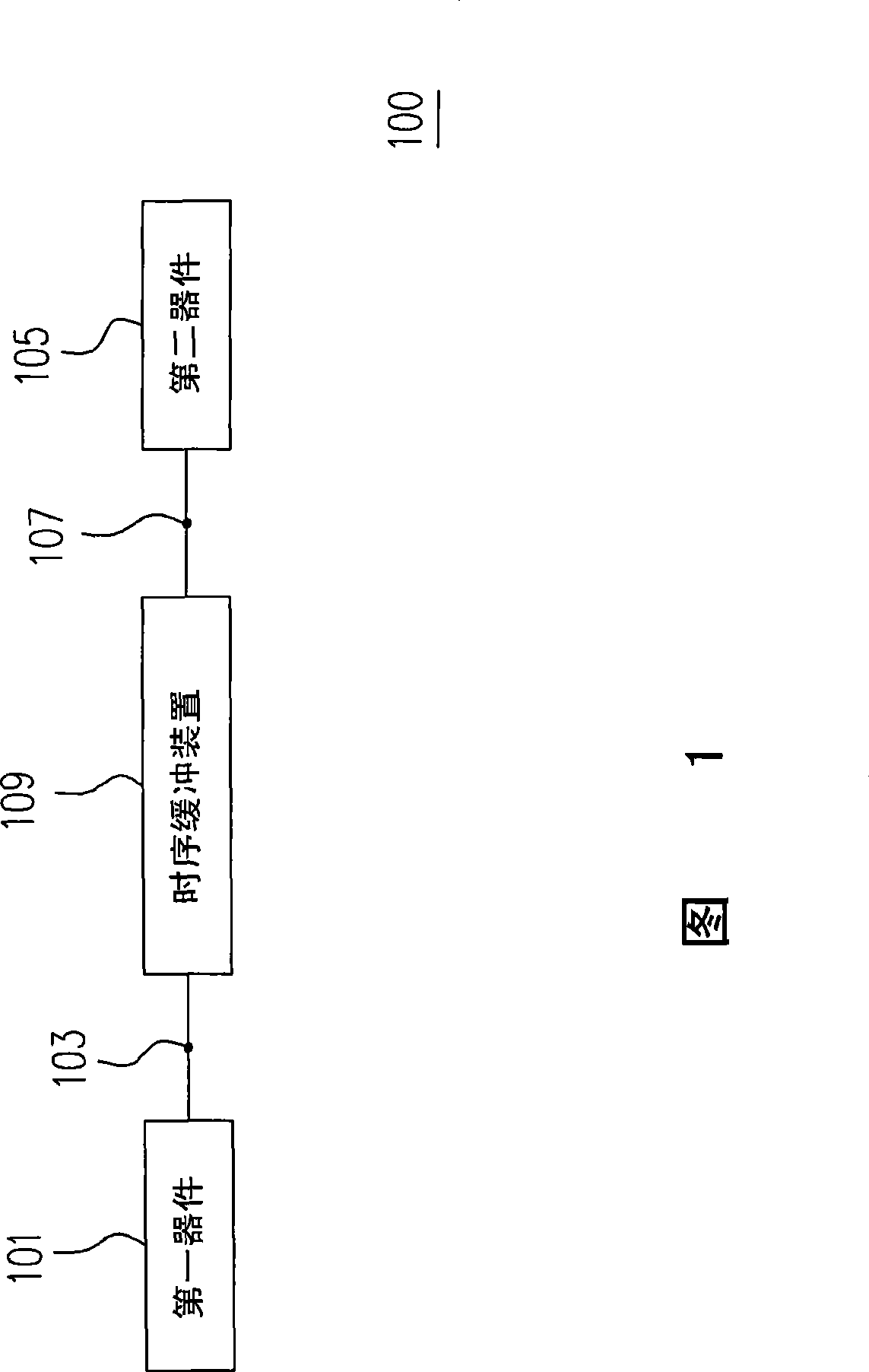

[0014] Please refer to FIG. 1 , which is a structural diagram of a compatible I2C bus and a system management bus according to an embodiment of the present invention.

[0015] The architecture 100 of the present invention compatible with the I2C bus and the system management bus includes a first device 101 , a second device 105 and a timing buffer device 109 . The first device 101 has an I2C bus interface 103 . The second device 105 has a system management bus interface 107 . The timing buffer device 109 is connected between the I2C bus interface 103 and the system management bus interface 107, and is used to make The data line on the system management bus interface 107 keeps the first state for a hold time and then changes to the second state, or makes the data line on the system management bus interface 107 change from the first state to the second state and then keeps the second state for one hold time. That is, because the I2C bus used by the first device 101 requires a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com