IC circuit with test access control circuit using a JTAG interface

A technology for access control and testing of access ports, applied in the direction of measuring electricity, measuring electrical variables, measuring devices, etc., can solve problems such as complex clock systems, and achieve the effect of solving synchronization problems and maintaining speed performance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

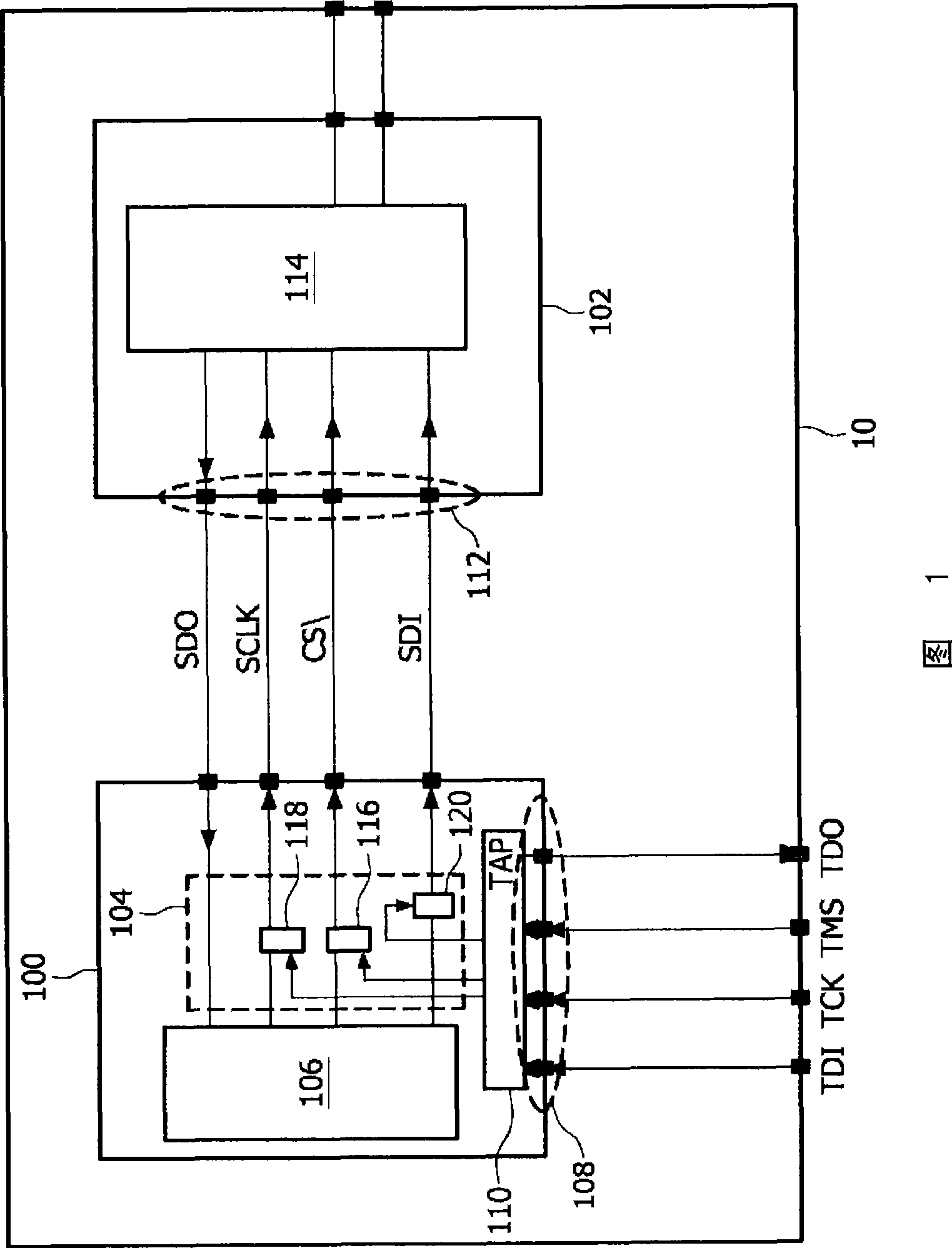

[0028] Referring to FIG. 1 , an integrated circuit 10 includes a first circuit portion 100 , a second circuit portion 102 , and a test access control (TAC) circuit 104 . The test access control circuit is shown schematically as part of the first circuit part, but it could of course be a separate circuit.

[0029] First circuit portion 100 includes digital core logic 106 , JTAG interface 108 and test access port (TAP) 110 . The JTAG interface 108 is a four / five-pin interface between the first circuit part 100 and the external pins of the integrated circuit 10, and is provided by each chip supporting the JTAG standard. According to the JTAG standard, JTAG interface 108 supports the following dedicated signals: Test Data In (TDI); Test Data Out (TDO); Test Clock (TCK); Test Mode Select (TMS);

[0030] "Test Reset" is an optional asynchronous reset signal and is not included in JTAG interface 108 of FIG. 1 . Although "test reset" is not shown in the embodiment of FIG. 1, the tes...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com