Memory control methods and circuit thereof

A technology of control circuit and control method, which is applied in the direction of static memory, digital memory information, information storage, etc., can solve problems such as impossibility to achieve optimal performance and fluctuation, and achieve the effect of optimal control performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

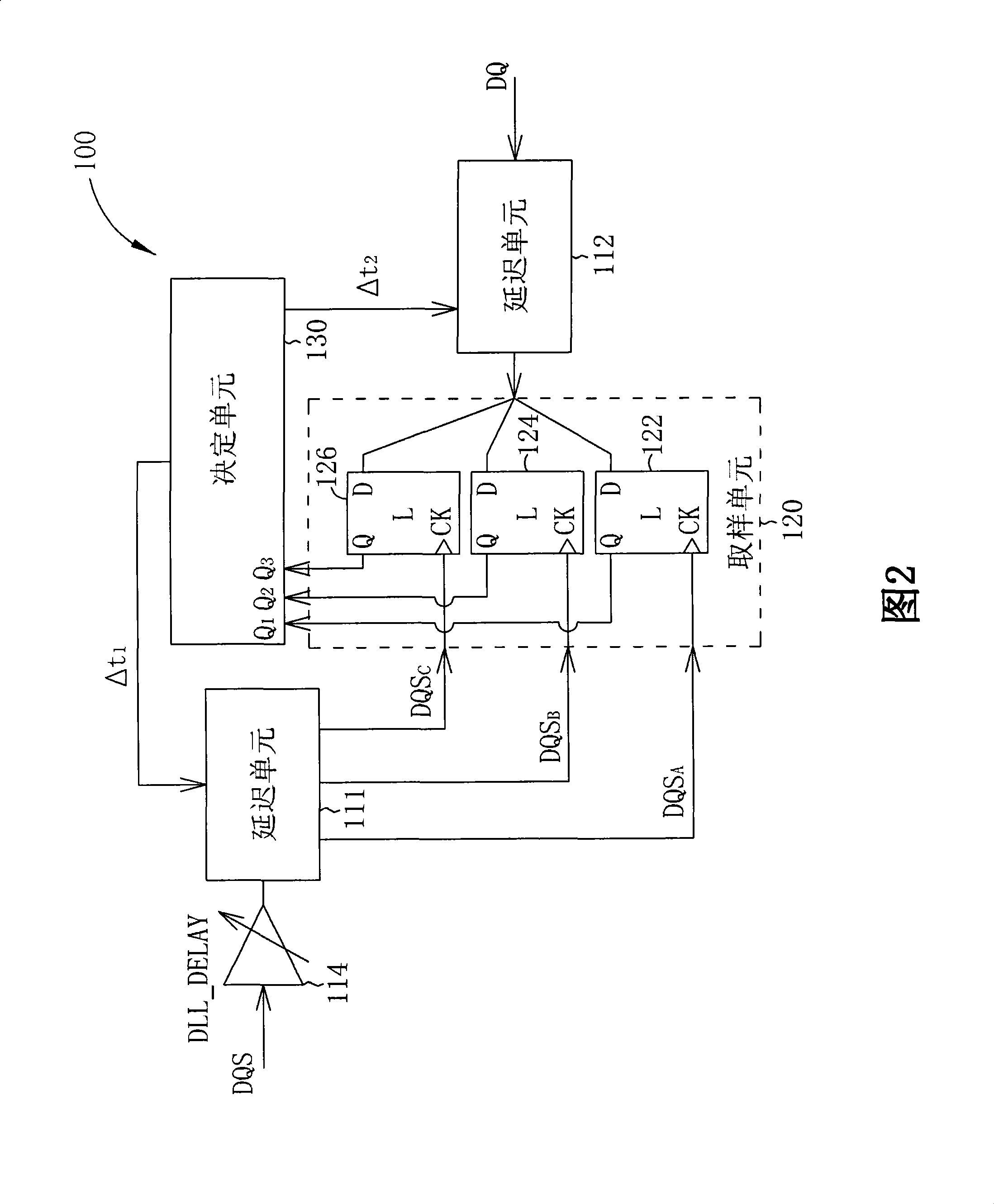

[0015] Please refer to FIG. 2 , which is a block diagram of a memory control circuit 100 according to a first embodiment of the present invention. In this embodiment, the memory control circuit 100 includes delay units 111 , 112 and 114 , a sampling unit 120 and a decision unit 130 . The memory control circuit 100 receives a data signal (such as a DQ signal) and a raw data strobe signal (such as a DQS signal) through the delay units 112 and 114 respectively. In addition, the delay unit 114 further includes a single delay cell (delay cell), as shown in FIG. 2 , the single delay cell has an adjustable delay value DLL_DELAY. The adjustable delay DLL_DELAY is set to a constant phase delay of 90 degrees. As shown in FIG. 2 , the sampling unit 120 includes latches 122 , 124 and 126 .

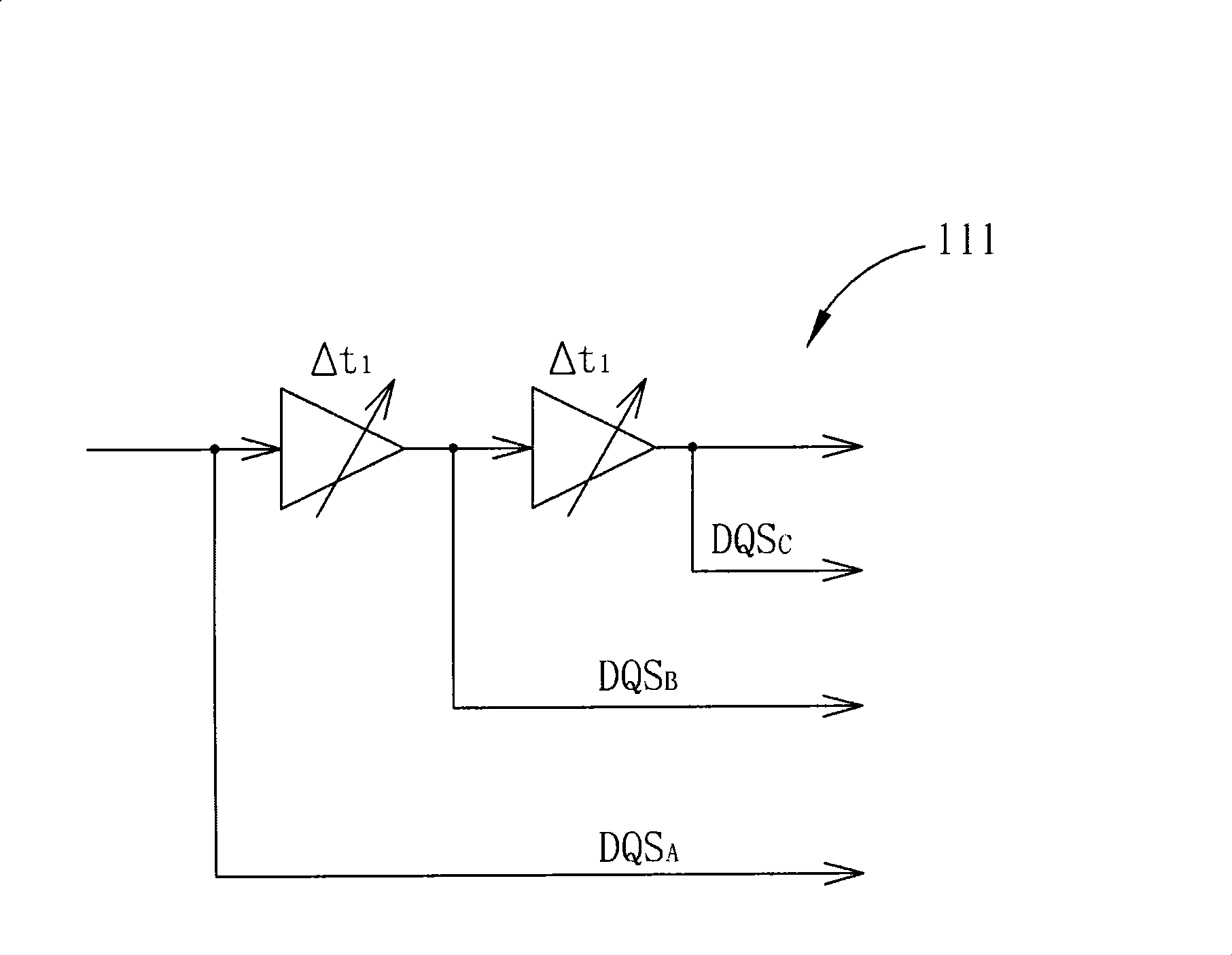

[0016] Please refer to Figure 2 and image 3 . image 3 is a schematic diagram of the delay unit 111 according to the first embodiment of the present invention. The delay unit 111 includes two de...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com