Method and circuit for loading on site programmable gate array

A technology of loading circuits and gate arrays, applied in the direction of program loading/starting, program control devices, etc., can solve the problems of limited clock rate control time, large data loading speed limit, affecting system initialization work, etc., to reduce the startup configuration. time, improve product performance and indicators, and reduce the effect of failure recovery time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

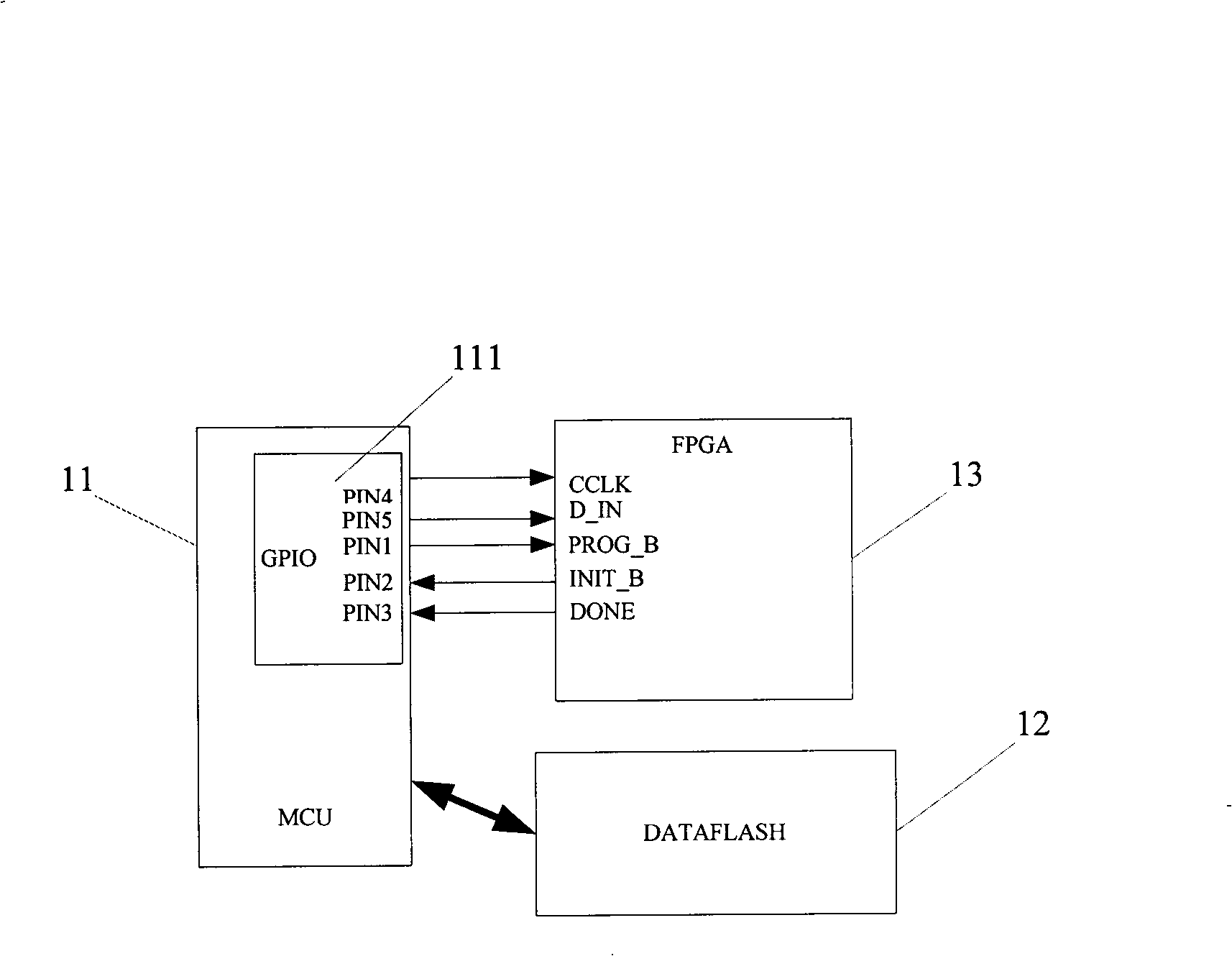

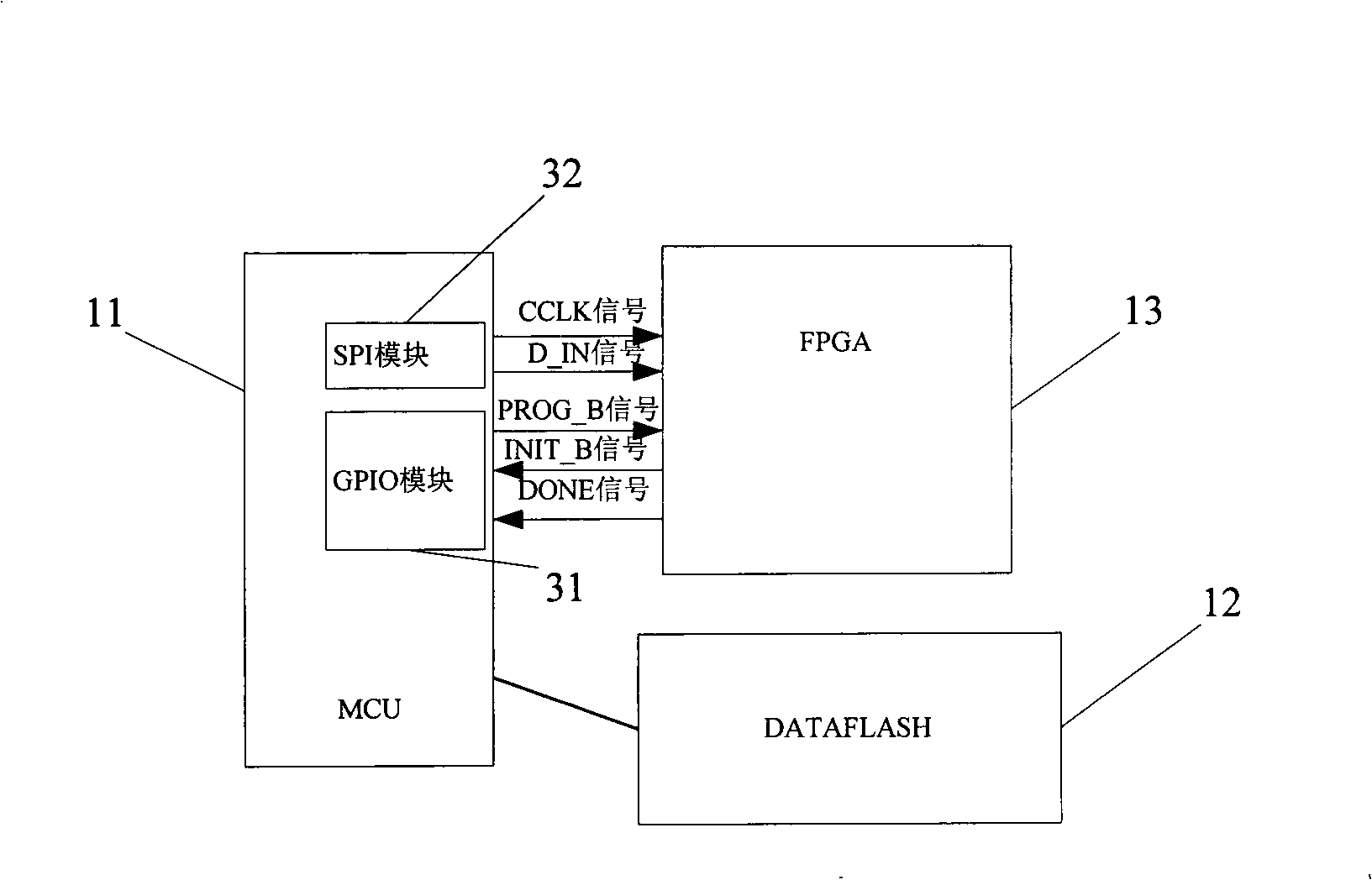

[0025] refer to figure 2 and image 3 , the present invention uses SPI (Serial Peripheral Interface, serial bus transmission interface) to the loading method and loading circuit of FPGA loading data to overcome the speed requirement to MCU pin. Such as image 3 As shown, MCU 11 is connected with FPGA 13 through GPIO 31 module and SPI 32 module. In one embodiment, the MCU 11 is connected to the DATAFLASH 12 through the bus, so as to quickly load the files stored in the DATAFLASH 12 to the FPGA 13 through the GPIO 31 module and the SPI32 module.

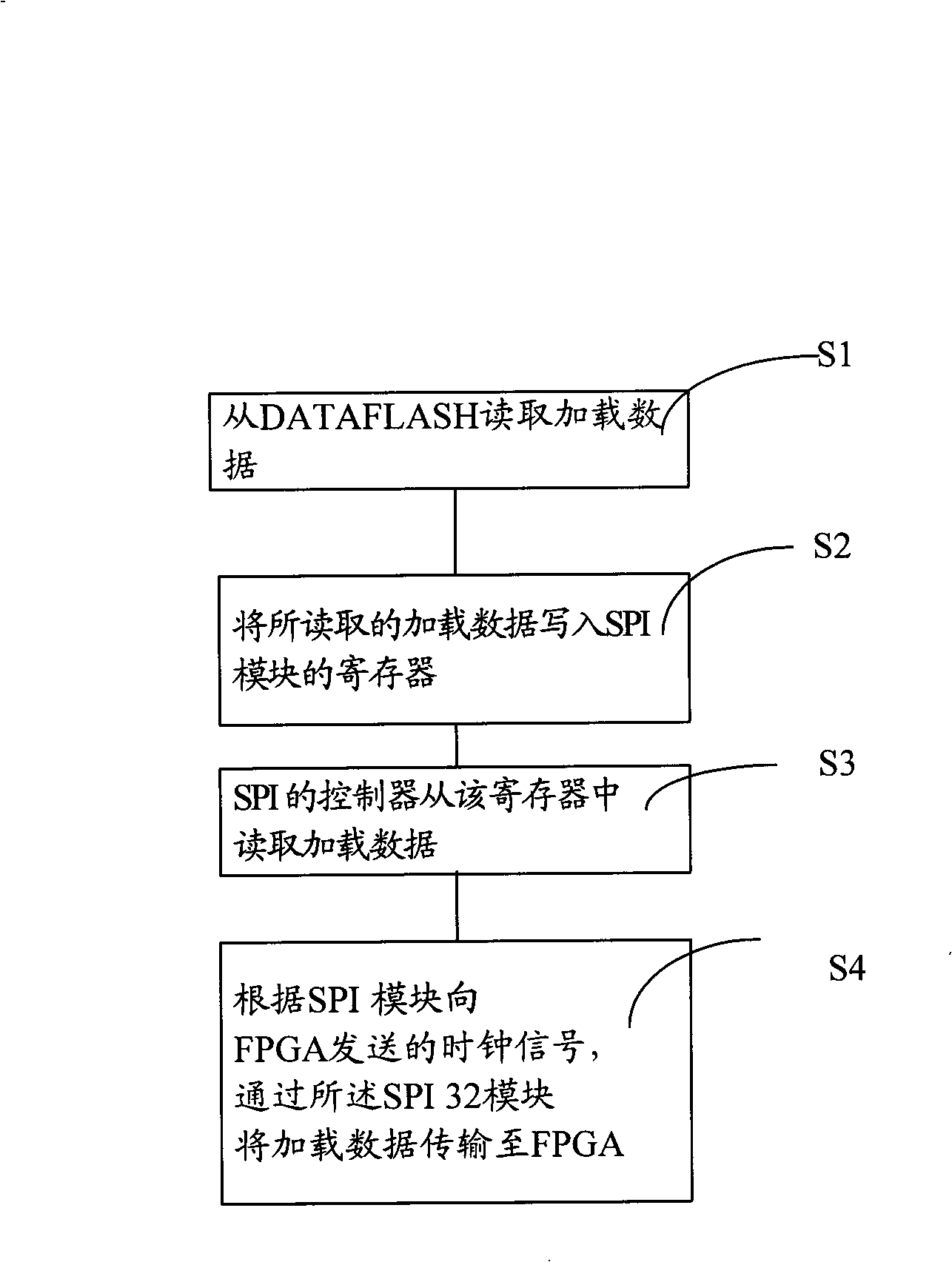

[0026] Such as figure 2 As shown, when loading data to FPGA 13, MCU 11 reads loading data (S1) from DATAFLASH12; Then writes the loading data read in the register of SPI 32 module (S2); The controller of SPI reads from this register In the present invention, send clock signal to FPGA 13 by SPI 32 module, according to the clock signal that SPI 32 module sends to FPGA 13, load data is transmitted to FPGA 13 by described SPI 32 modu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com