Deep-submicron CMOS process inductively compensated photoelectric detector and its manufacturing method

A photodetector and deep submicron technology, which is applied in the fields of electric solid-state devices, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems that cannot meet the scaling down of transistors, and achieve improved dark current characteristics, improved response speed, and improved Effects of Responsiveness Properties

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

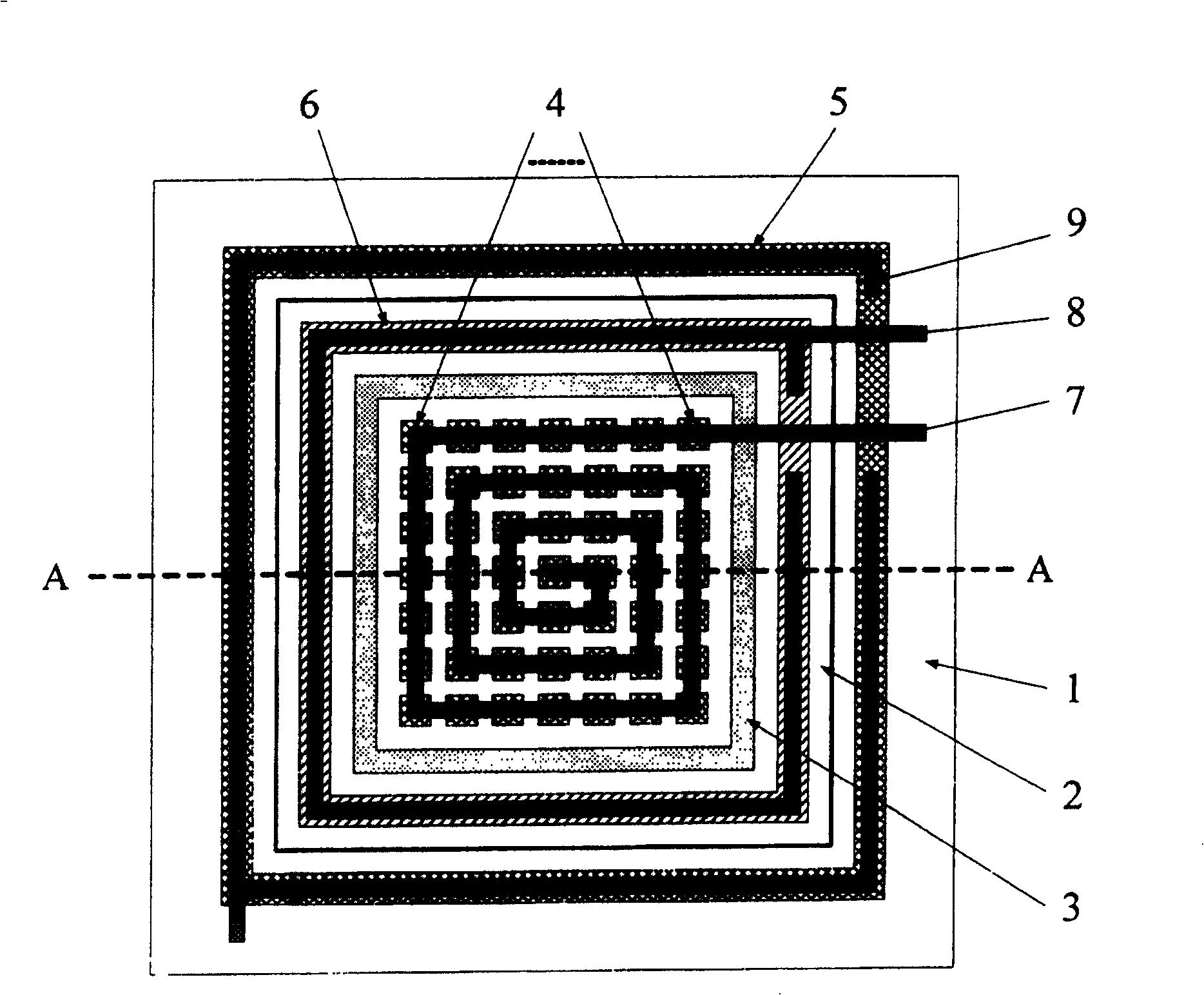

[0081] The production technology used for the photodetector designed in the present invention is all provided by the deep submicron CMOS technology, without any special requirements on the technology. Further set forth the present invention below in conjunction with embodiment and accompanying drawing:

[0082] 1. Fabricate an N well 2 with an area of 70 μm×70 μm on the P substrate 1 ; and prepare it simultaneously with the N well of the PMOS transistor. The depth is about 0.95μm, and the injection concentration is about 1×10 17 cm -3 .

[0083] 2. Forming an annular shallow trench isolation region 3 in the N well region 2 . The depth is about 0.8 μm, the width of the ring is 1 μm, and the outer edge of the ring is 3.5 μm away from the edge of the N well region 2 .

[0084] 3. Fabricate the array-shaped first P+ region 4 in the N well region 2 . Doping concentration is about 1×10 20 cm -3 . The array size is 7×7, the area of each unit in the array is 6 μm×6 μm, and...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com