Drive circuit and drive method for panel display device

a technology of drive circuit and display device, which is applied in the direction of static indicating devices, instruments, electroluminescent light sources, etc., can solve the problems of uneven display and deteriorated emission intensities, and achieve the effect of increasing charging speed and speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

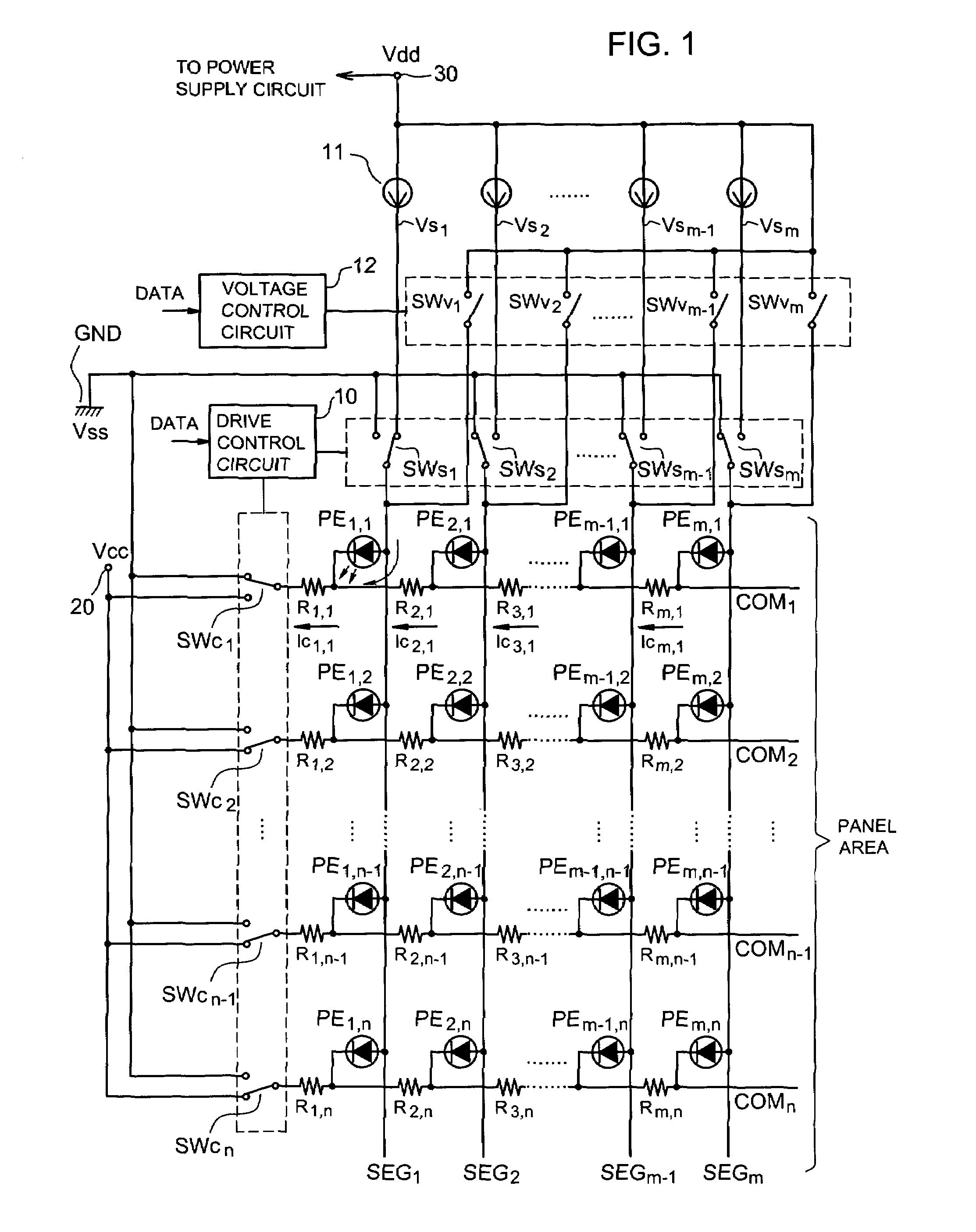

[0020]FIG. 1 is a block diagram illustrating a drive circuit for a panel display device which is the present invention. The organic EL panel display device has light-emitting devices, or organic EL devices PEP,Q (P is an integer ranging from 1 to n; Q is an integer ranging from 1 to m), which are arranged at respective intersections between a plurality of data lines (anode lines) SEG1 to SEGm and a plurality of scan lines (cathode lines) COM1 to COMn (m and n are integers no smaller than 2).

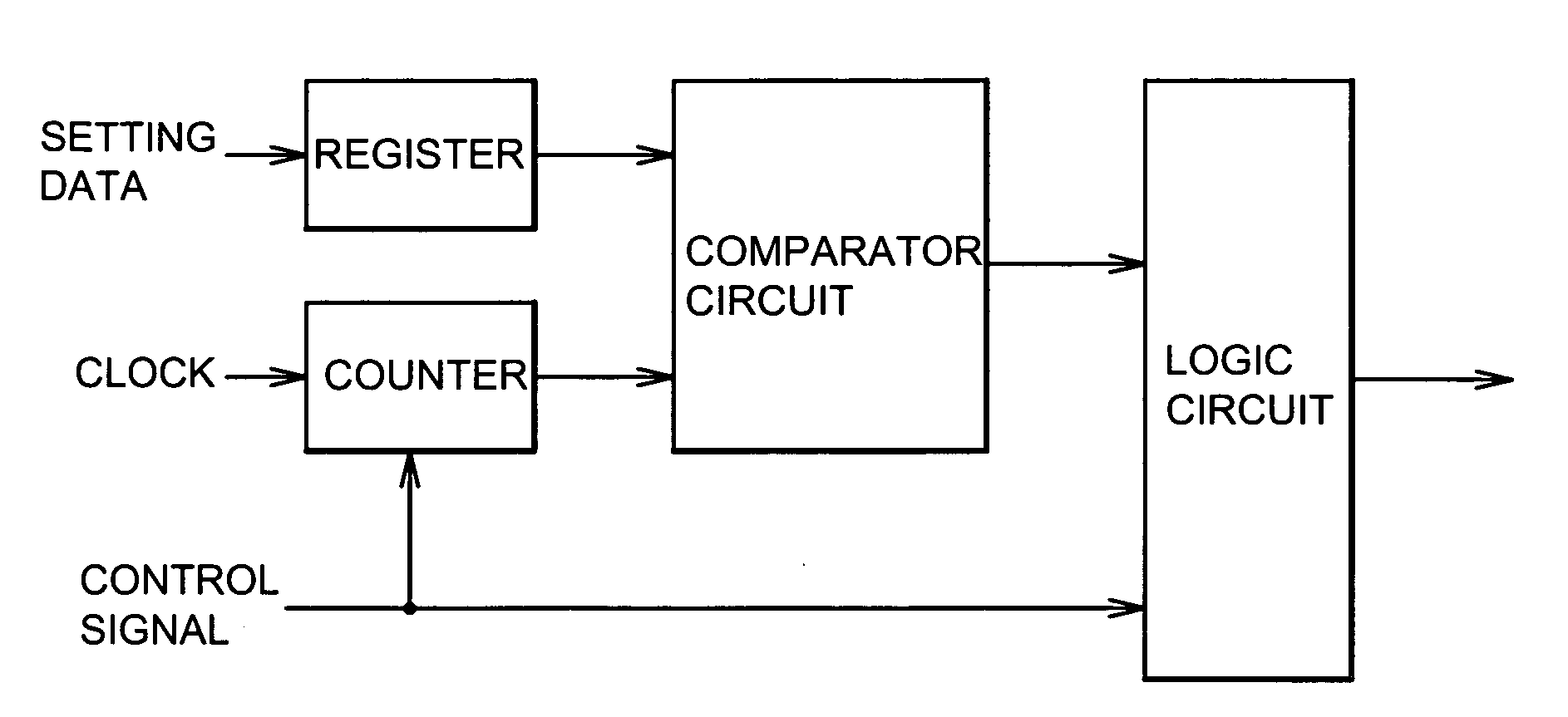

[0021]The drive circuit for the panel display device according to the present invention comprises first switch circuits SWsP, second switch circuits SWcQ, and third switch circuits SWvP. The first switch circuits SWsP connect the data lines SEGP to either respective constant current sources 11 or a ground potential Vss. The second switch circuits SWcQ connect the respective scan lines COMQ to either one of a scan line power supply 20 (power supply potential Vcc) and the ground voltage Vss. The th...

second embodiment

[0031]Next, with reference to the timing chart shown in FIG. 8, description will be given of the operation of driving a panel display device which is the present invention.

[0032]Here, the drive circuit for the panel display device may be configured the same as in the first embodiment of the present invention.

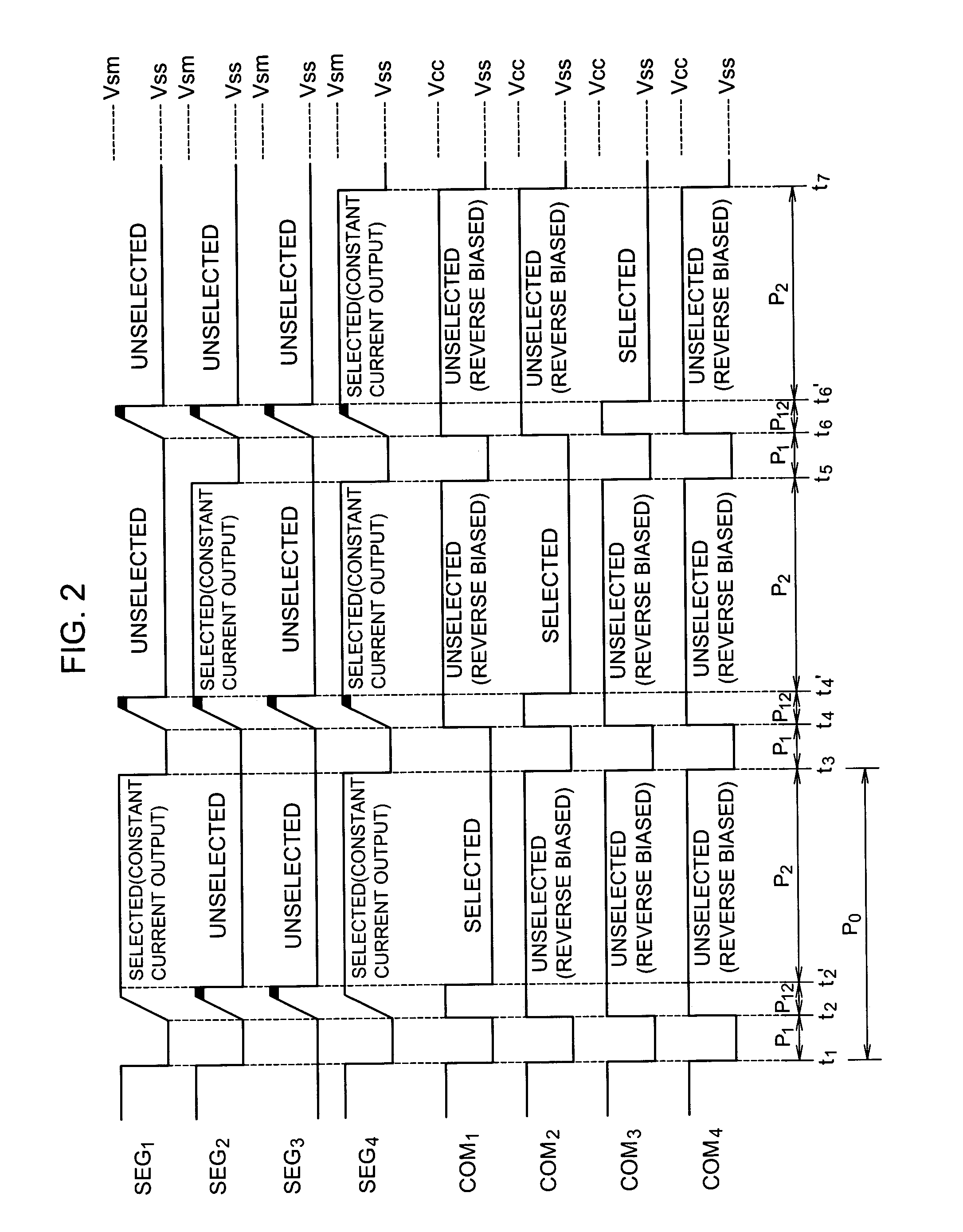

[0033]In the period P1, the switch circuits SWsP are turned OFF as shown in FIG. 4. The switch circuit SWc1 is connected to the power supply potential Vcc. Then, the voltage control circuit 12 turns ON the switch circuits SWvP to charge the loads of the organic EL devices PEP,Q up to a certain potential (target potential Vsm). Consequently, discharging is achieved in H level.

[0034]Subsequently, in the period P2, as shown in FIG. 5, the voltage control circuit 12 turns OFF the switch circuits SWvP, so that the potentials of the data lines SEGP are kept at a certain potential (Vsm±α; α is arbitrary). At time t4, as shown in FIG. 6, the switch circuit SWs2 is connected to the const...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com