Processor and method for trans-boundary aligned multiple transient memory data

A temporary register and cross-boundary technology, applied in the field of data processing, can solve the problems of processor pipeline stop, waste of bus bandwidth, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

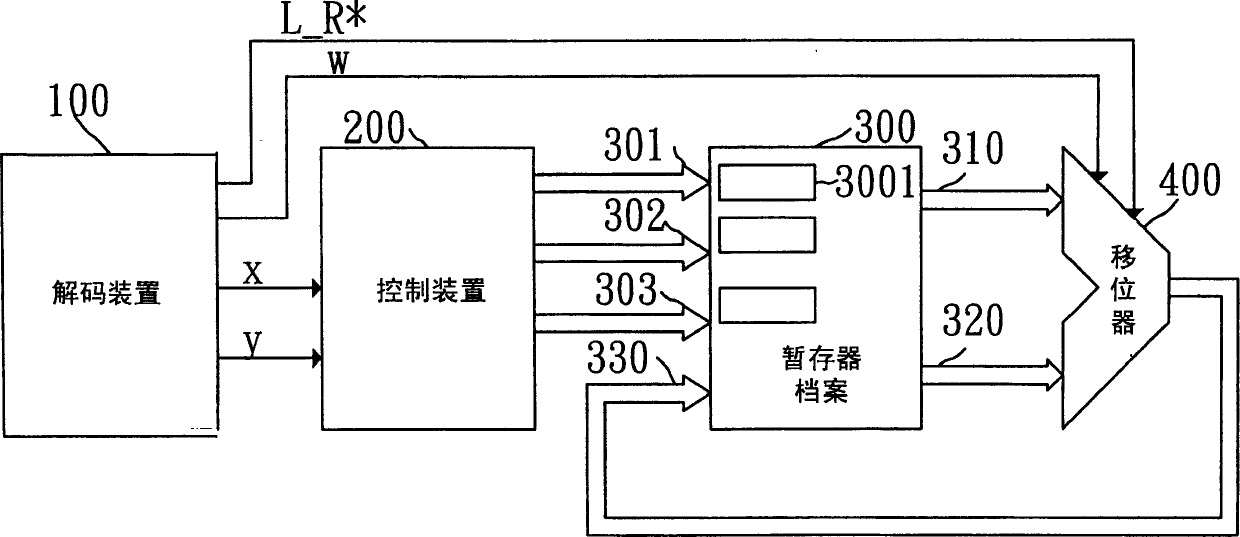

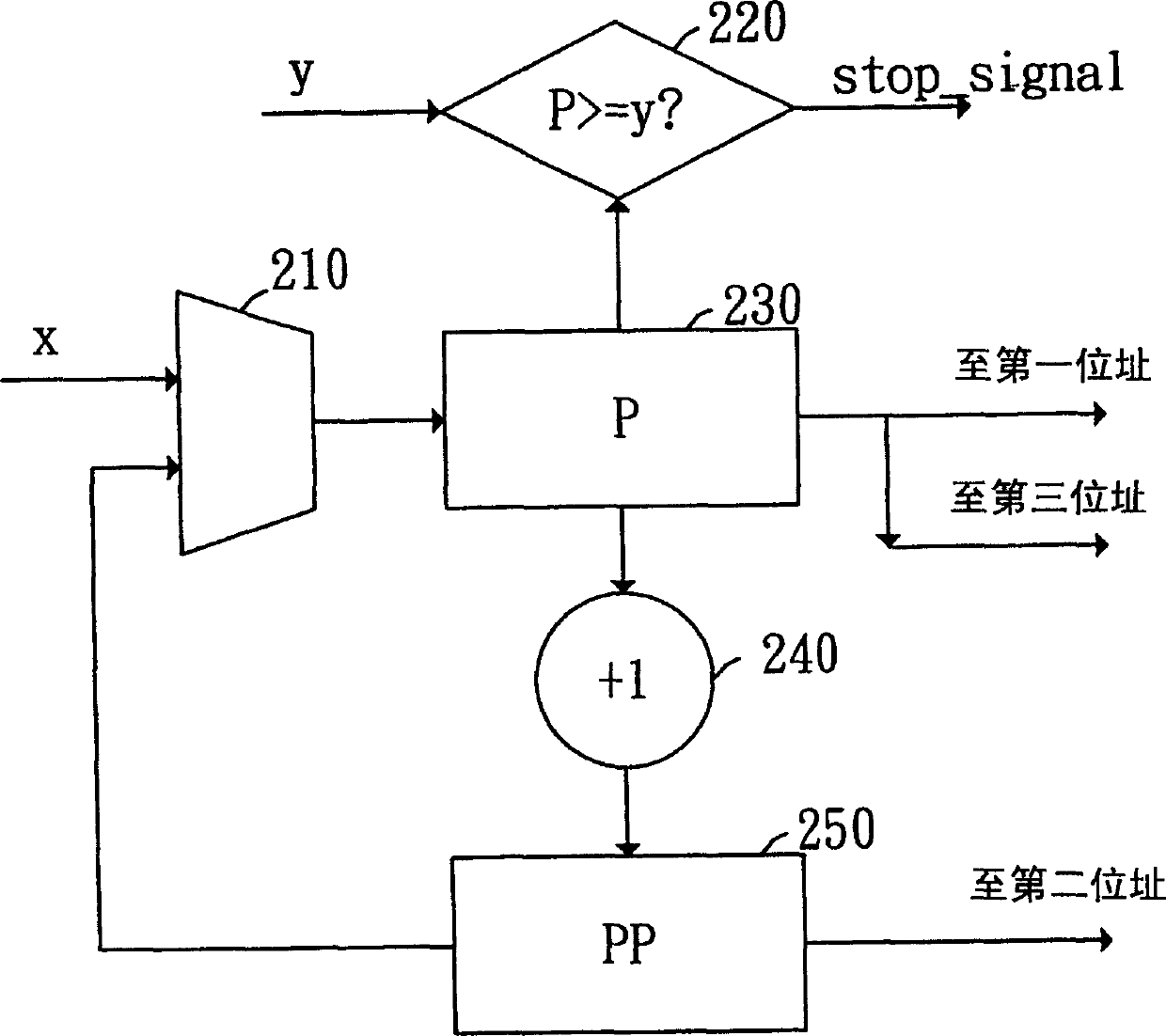

[0035] FIG. 4 shows a block diagram of a processor utilizing cross-boundary aligned complex register data according to the present invention, which includes a decoding device 100 , a control device 200 , a register file 300 and a shifter 400 . The register file 300 has a plurality of registers 3001, and each register 3001 has N bits. In this embodiment, the value of N is preferably 32. The temporary register file 300 can read the temporary register 3001 according to a first address 301 and a second address 302 respectively, and output from a first output terminal 310 and a second output terminal 320, and can be output according to a The third address 303 is written into one of the multiple registers 3001 through an input terminal 330 (N is a positive integer).

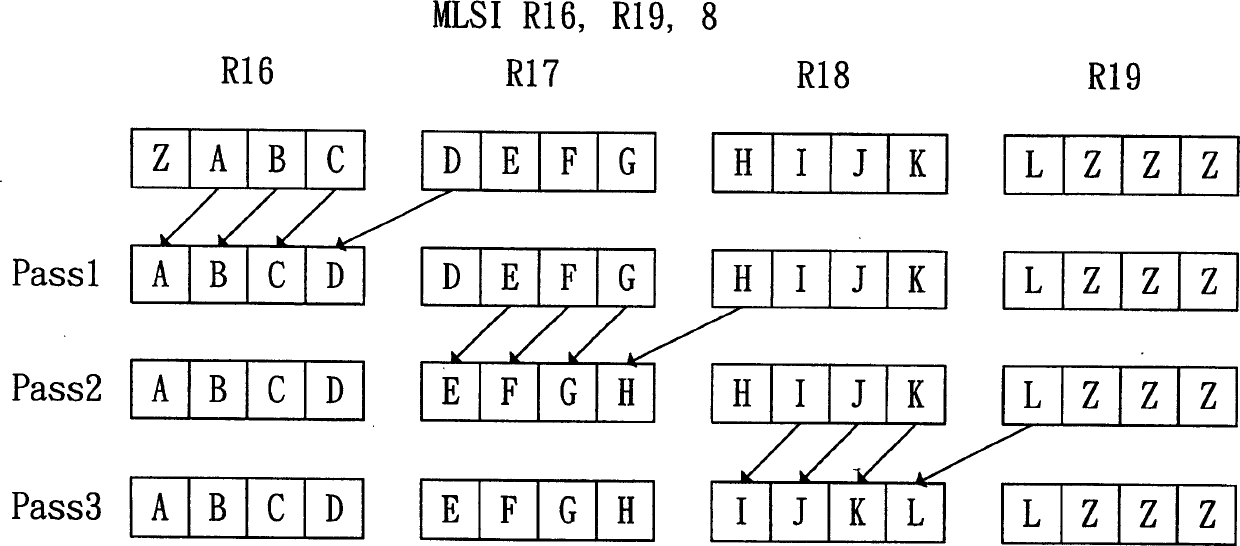

[0036] The decoding device 100 decodes a multiple shift instruction, which can be divided into a multiple left shift instruction (Multiple Left Shin Instruction, MLSI) and a multiple right shift instruction (Multiple R...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com