A structure optimization design method of to packaged power semiconductor device

A power semiconductor and optimization design technology, applied in the field of TO package power semiconductor device structure optimization design, can solve problems such as hindering the application of engineering optimization algorithms, and achieve the effect of easy understanding, good applicability, and clear steps

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0056] Below in conjunction with embodiment, the present invention is described further, but does not constitute any restriction to the present invention, any limited number of modifications done in the scope of claims of the present invention is still within the scope of claims of the present invention.

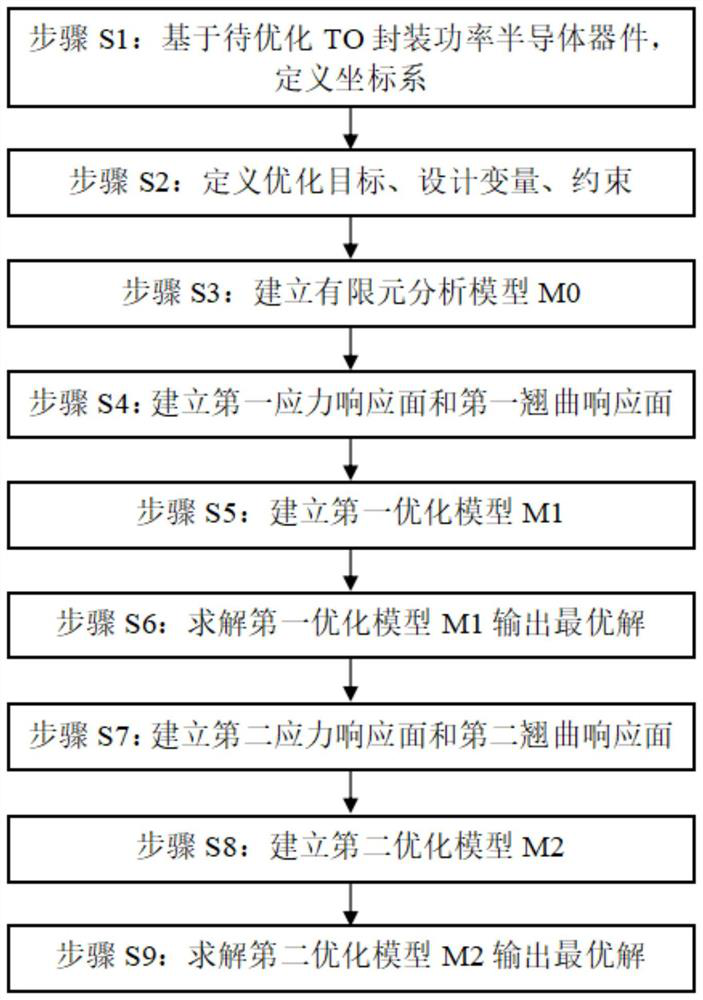

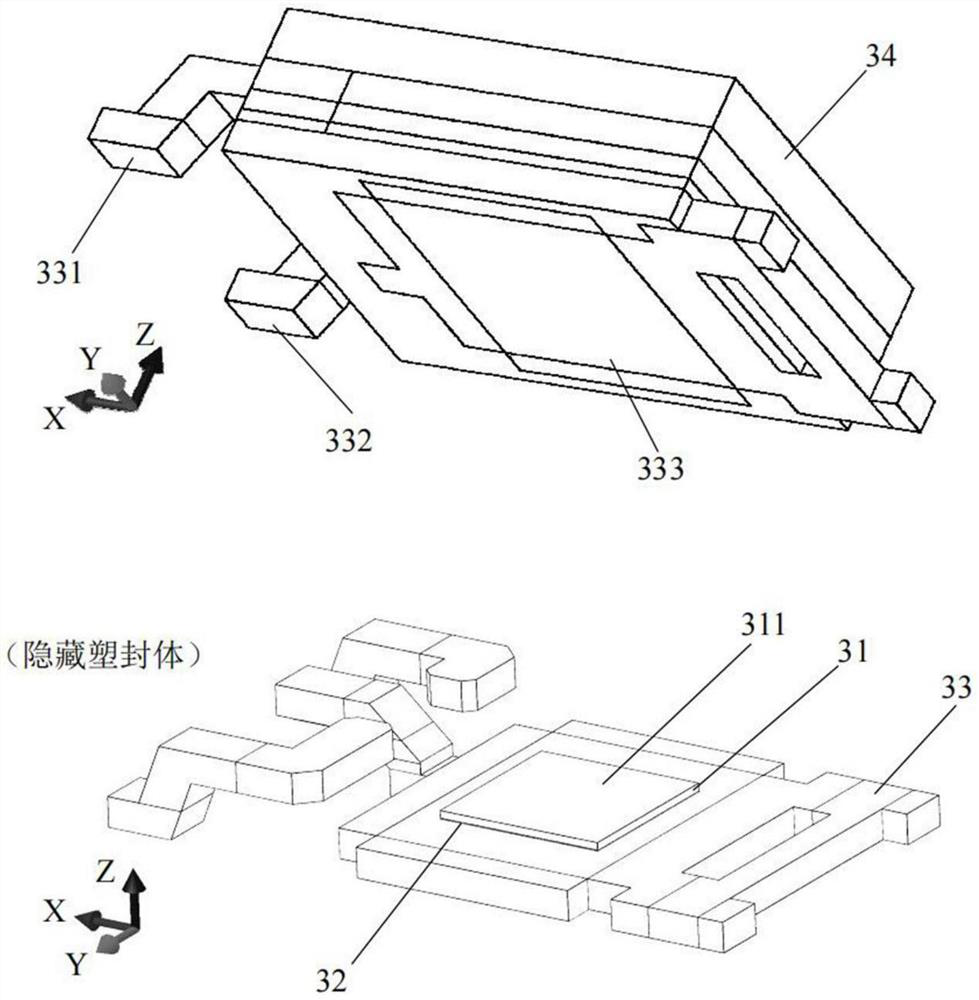

[0057] Such as figure 1 — image 3 As shown, the present invention provides a method for structural optimization design of a TO package power semiconductor device, the method comprising the following processing steps:

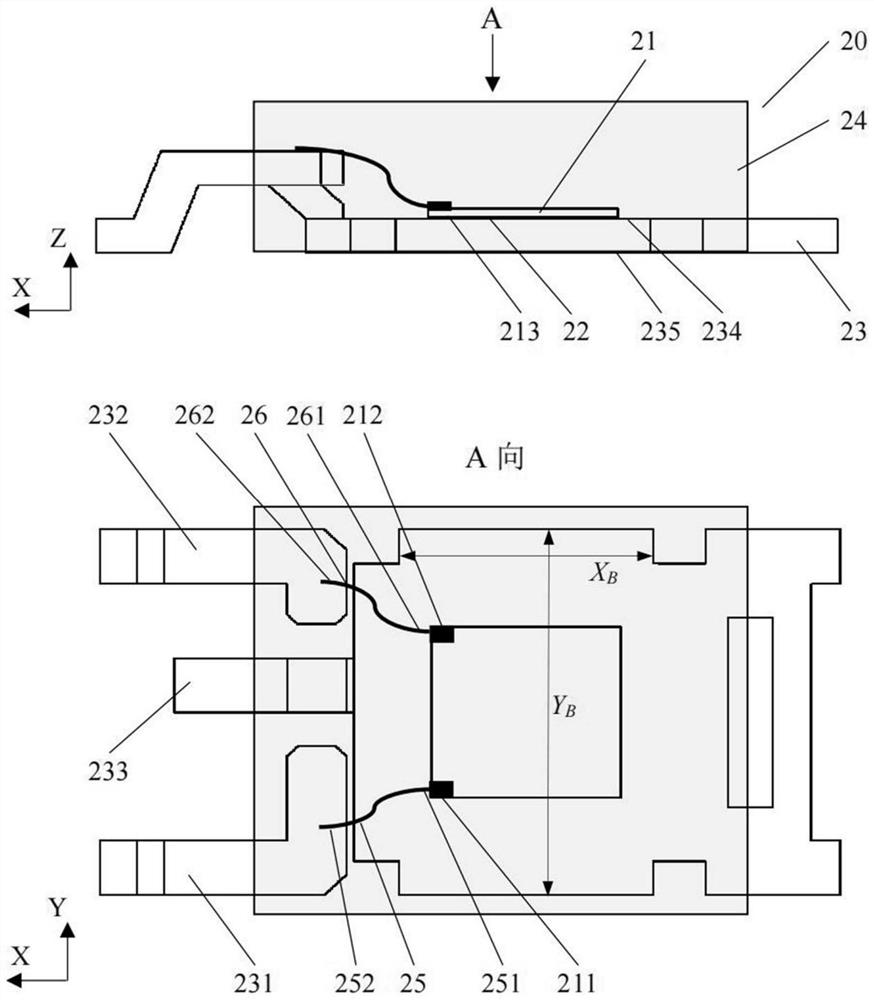

[0058] Step 1: Define the coordinate system based on the TO package power semiconductor device to be optimized. Such as figure 2 As shown, the package model of the TO package power semiconductor device 20 to be optimized is TO-252, including a chip 21 , a solder layer 22 , a lead frame 23 , a plastic package 24 , a first bonding wire 25 , and a second bonding wire 26 . The lower surface 213 of the chip is connected to the upper surface 234 of the base of ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com