A fpga efficient rule matching method and terminal

A matching method and rule technology, applied in transmission systems, electrical components, etc., can solve problems such as hash conflicts, identical hash values, and different inputs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

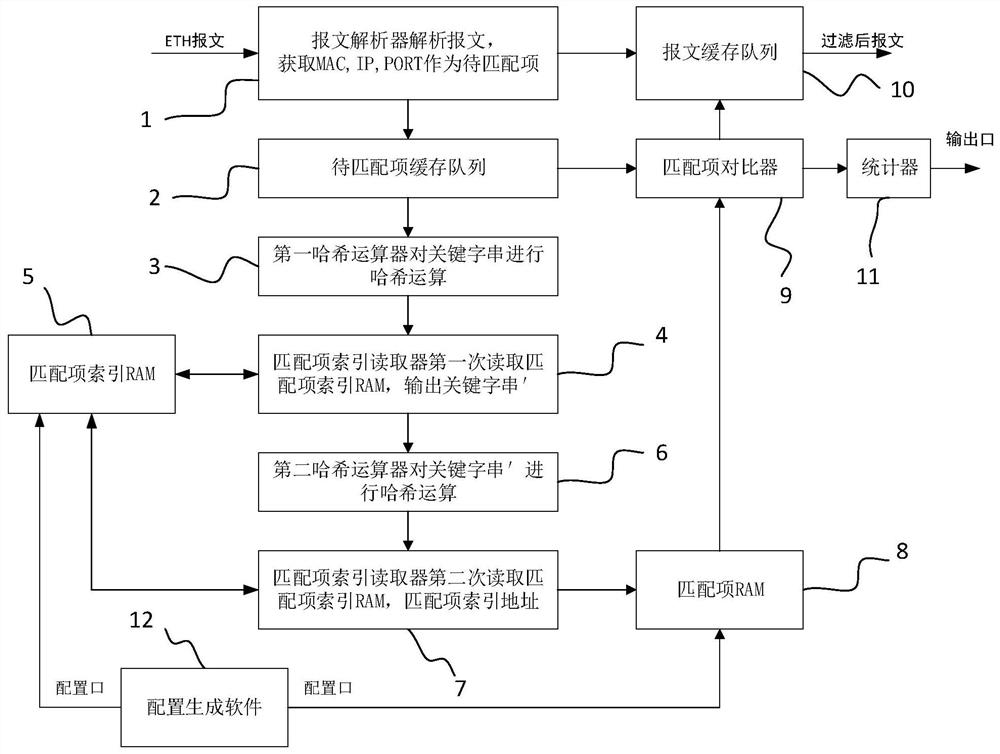

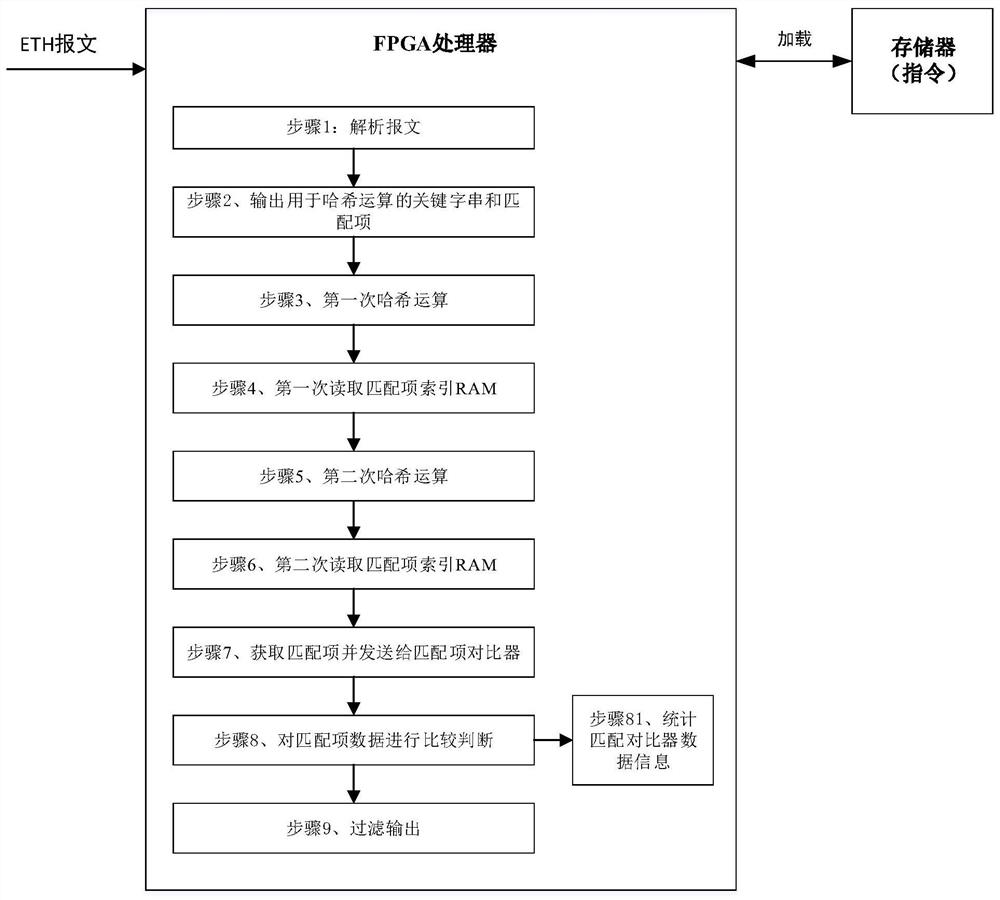

[0062] Such as figure 1 As shown, an FPGA efficient rule matching method includes the following steps:

[0063] Step 1. Parse the message

[0064] The message parser 1 parses the message from Ethernet, and extracts the source MAC address, destination MAC address, source IP address, destination IP address, source port number, destination port number, etc. in the message as information to be matched, And the information of the item to be matched is output to the cache queue 2 of the item to be matched, and at the same time, the message is output to the message cache queue 10;

[0065] Step 2. Output the keyword string and matching items used for hashing:

[0066] Described to-be-matched item cache queue 2 outputs keyword string to first hash operator 3, is used for hash operation, and described to-be-matched item information is exported to matching item comparator 9; Described keyword string is One piece of matching item information or a combination of multiple matching item in...

Embodiment 2

[0088] Such as Figure 1-2 As shown, an FPGA efficient rule matching terminal includes a memory, and the memory stores a plurality of instructions, and the instructions are suitable for loading and executing by the FPGA processor, and the execution steps are as follows:

[0089] Step 1. Parse the message

[0090] The message parser 1 parses the message from Ethernet, and extracts the source MAC address, destination MAC address, source IP address, destination IP address, source port number, destination port number, etc. in the message as information to be matched, And the information of the item to be matched is output to the cache queue 2 of the item to be matched, and at the same time, the message is output to the message cache queue 10;

[0091] Step 2. Output the key string and matches for the hash operation

[0092] Described to-be-matched item cache queue 2 outputs keyword string to first hash operator 3, is used for hash operation, and described to-be-matched item info...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com